Dec., 2024

碳基电子器件及应用

**DOI:**10.12450/j.gtdzx.202406008

# GaN器件金刚石近结集成热管理技术研究进展®

郭怀新<sup>1,2\*\*</sup> 陈堂胜<sup>1,2</sup> 孔月婵<sup>1,2</sup> 李忠辉<sup>1,2</sup> 李义壮<sup>1,2</sup> 黄 健<sup>1,2</sup> (<sup>1</sup>固态微波器件与电路全国重点实验室,南京,210016) (<sup>2</sup>南京电子器件研究所,南京,210016) 2024-11-13收稿,2024-11-20收改稿

摘要:GaN器件大功率及高功率密度的发展受限于其自生热和近结区散热能力引起的器件结温升高问题,导致器件性能严重下降,GaN器件的大功率潜能远未得到发挥,金刚石近结集成热管理技术是解决GaN器件热瓶颈的重要途径。本文详细论述GaN器件近结热管理技术的重要性,并对近年来国际上正在开展的金刚石近结散热技术方法进行系统分析和评述,揭示了金刚石与GaN器件近结集成工艺途径及面临的技术挑战,阐述了GaN器件金刚石近结集成热管理的技术现状和发展方向。

关键词:GaN功率器件;器件级热管理;热测试;金刚石衬底;金刚石钝化

中图分类号:TN386 文献标识码:A 文章编号:1000-3819(2024)06-0561-07

# Research Progress of Diamond Near-junction Integrated Thermal Management for GaN Devices

GUO Huaixin<sup>1,2</sup> CHEN Tangsheng<sup>1,2</sup> KONG Yuechan<sup>1,2</sup> LI Zhonghui<sup>1,2</sup> LI Yizhuang<sup>1,2</sup> HUANG Jian<sup>1,2</sup>

(¹ National Key Laboratory of Solid-state Microwave Devices and Circuits, Nanjing, 210016, CHN)

(² Nanjing Electronic Devices Institute, Nanjing, 210016, CHN)

**Abstract:** The development of high power and high-power density for GaN devices is limited by the synergism of self-heating effect and heat dissipation capabilities in the near junction region, which leads to an increase in device junction temperature and a serious decline in device performance. As a result, the high-power potential of GaN devices has not been fully realized. Diamond near-junction integrated thermal management technology is an important way to solve the thermal bottleneck of GaN devices. The importance of near junction thermal management technology for GaN devices is dissipation in detail, the research progress of foreign advanced diamond near junction heat dissipation technology are analyzed and evaluated systemically in this paper. Meanwhile, the integrated process approach and technical challenges of the integration between diamond and near junctions of GaN devices are expounded, and the state and direction of diamond near junction integrated thermal management technology for GaN devices is also explained.

Key words: GaN power devices; device level thermal management; thermal testing; diamond substrate; diamond passivation

<sup>\*</sup> 基金项目:国家自然科学基金重大研究计划项目(92373118)

<sup>\*\*</sup> 联系作者:E-mail:guohuaixin@163.com

#### 引 言

GaN作为第三代半导体材料的代表,具有优异 的电子饱和速度、耐击穿场强、禁带宽度等独特优 势,使得GaN HEMT 功率器件综合特性远优于 GaAs为主的第二代半导体器件,极适用于固态大功 率器件及高频微波器件,广泛应用于雷达、基站及移 动通信等领域。然而,随着新一代信息化系统对大 功率、高集成发展的迫切需求,对GaN器件的大功率 及高功率密度提出了更高的要求,这种高功率或者 高功率密度下的热积累导致GaN器件的性能和可靠 性急剧下降,且受GaN器件散热结构和自身材料传 热能力限制,使得GaN器件的大功率潜能远未得到 发挥[1-3]。因此,热积累问题已成为制约现阶段 GaN 器件应用和发展的主要技术瓶颈之一,尤其是2022 年美国国防高级研究计划局(Defense Advanced Research Projects Agency, DARPA)再次提出 GaN 功 率器件功率密度指标达到81 W/mm的研究计划,远 高于目前 GaN 器件的功率密度(≤20 W/mm),对 GaN 器件的热管理技术提出了更高的挑战[1-6]。综上 所述,器件级热管理技术已成为GaN功率器件开发 及应用的关键技术之一和业内主要研究热点。

固体电子学研究与进展

#### 金刚石近结集成热管理技术分析 1

#### 1.1 GaN器件近结集成热管理意义

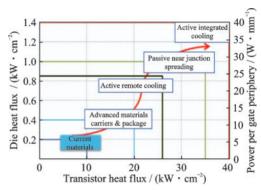

GaN器件热积累瓶颈是指器件在大功率或高 功率密度工作状态下因结温升高导致的器件输出 特性下降和器件寿命衰减现象,甚至直接导致器件 损坏。功率密度越大,器件内部热积累愈加严重, 直接导致 GaN 大功率潜能远未得到发挥,传统封装 及系统层级热管理难以满足GaN器件高功率密度 的散热需求。量化的GaN器件功率栅密度(Power per gate periphery)与各类散热技术之间的理论关系 图[1-3,7]如图1所示,可以看出,现有的封装级主被动 结合的散热技术最大可实现 20 W/mm 的功率输出 能力。基于美国 DARPA 的牵引计划, GaN 器件的 功率输出目标为81 W/mm,因此,开展新型器件级 热管理技术研究已迫在眉睫。

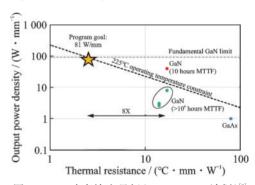

美国 DARPA 于 2012年在国际上首次布局 GaN 器件内近结热管理技术,率先牵引"近结热输 运(Near junction thermal transport, NJTT)"项目研 发,利用高导热金刚石衬底代替传统SiC衬底,进一 步提升GaN功率器件近结区的热输运能力,满足 GaN 器件更高功率密度的散热[1-3]。 2022 年 DAR-PA 再进一步布局器件级电子散热技术(Technologies for heat removal in electronics at the device scale, THREADS)[8],如图2所示,重点通过高导热 材料近结集成和热结构优化技术开发,解决GaN功 率器件内部散热问题,旨在发挥GaN器件大功率潜 能,提升雷达射频功率输出能力。

44卷

图1 热管理技术散热能力分析[7]

Analysis of heat dissipation capacity of thermal man-Fig.1 agement technologies<sup>[7]</sup>

图 2 GaN 功率输出目标(THREADS 计划)[8]

Fig.2 The target of GaN power output (THREADS program )[8]

## 1.2 GaN器件金刚石近结热管理设计

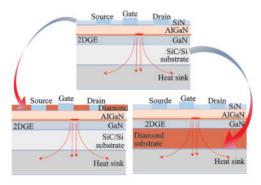

GaN器件内部热积累瓶颈的本质是GaN器件 自身工作时产生大量热而材料传热能力不足。 GaN 功率器件的工作取决于 AlGaN/GaN 异质结的 二维电子气,热效应的产生主要是工作时二维电子 气沟道区域不可避免的产生热功耗,而这种热功耗 的传输途径主要是GaN势垒层和衬底层传递至封 装热沉层从而耗散掉,而GaN器件内部结构材料的 传热能力满足不了所产生的热功耗的传输时,器件 工作区的温度就会升高,这种热效应直接导致GaN 器件输出特性和寿命的下降[1-8]。因此,GaN器件内 部结构材料的传热能力成为器件级热管理技术的 关键因素。金刚石近结集成结构是用金刚石高导

热材料替换传统 GaN 器件的 SiC 或 Si 衬底,或者是替换传统 GaN 器件的 SiN 钝化层,进而将高导热材料集成到 GaN 器件热源区附近,通过金刚石材料的高导热特性提升 GaN 器件内部传热能力,如图 3 所示,解决热源区热量不断积累问题。

图 3 金刚石近结散热结构设计

Fig.3 Design of diamond near junction heat dissipation structure

金刚石近结集成热管理技术具有极大的创新性 和难度,其金刚石传热结构设计、集成界面及工艺评估、集成工艺兼容性等关键技术开发都极具挑战性。

# 2 GaN器件金刚石近结热评估技术

## 2.1 GaN器件结构热设计技术

GaN器件传热结构设计不仅包括对GaN器件金刚石近结集成结构设计,还包括对GaN器件本征结构的势垒层、缓冲层进行耦合设计,达到揭示金刚石近结集成散热机理、管控金刚石集成工艺质量、优化和评估金刚石近结集成结构的目的。

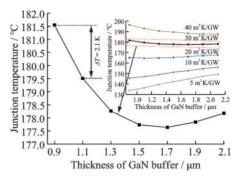

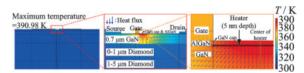

在该技术方向的研究是通过多物理场仿真计 算技术实现,最具有代表性的是2017年南京电子器 件研究所及 2023年 Sungkyunkwan University 报道 的研究工作。南京电子器件研究所团队在国内率 先报道了金刚石衬底GaN器件内部各层结构对散 热能力的影响分析,提出了GaN过渡层对器件散热 能力的影响受金刚石/GaN界面层热阻的影响机 理,最先发现 GaN 缓冲层存在最优值,如图 4 所 示[9]。Sungkyunkwan University团队则分析了金刚 石近结集成GaN器件热流密度变化规律,如图5所 示[10],拟合给出散热能力的影响因素定量公式,为 金刚石近结集成热管理的设计提供了更为直观的 分析方法。目前,该技术的难点是多因素的耦合设 计复杂,仿真计算时间长,系统分析难度大。因此, 金刚石近结集成GaN器件的多层级材料结构、材料 热物性等多种因素自身及之间的耦合作用、耦合影 响机制和规律的定量仿真评估,目前还未有较为全面及系统的研究报道。

图 4 GaN缓冲层最优值与界面热阻关系<sup>[9]</sup>

Fig.4 The optimal value of GaN buffer layer and its relationship with interfacial thermal resistance<sup>[9]</sup>

图 5 金刚石近结散热热流密度分布[10]

Fig. 5 Distribution of heat flux density for diamond near junction heat dissipation<sup>[10]</sup>

#### 2.2 GaN 器件集成界面及金刚石热测试技术

金刚石近结集成 GaN 器件的集成界面传热能力和金刚石材料的传热能力直接影响了金刚石近结集成热管理的应用价值,因此,在工艺开发过程中,对 GaN 器件集成界面及金刚石传热能力的管控极为重要。因此美国 DARPA 在进行热管理技术项目牵引过程中,热测试方法的研究也是项目的重要内容之一。

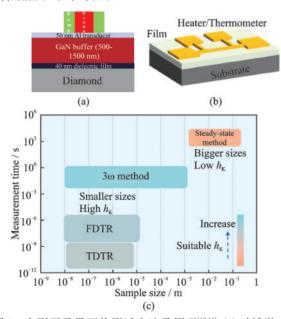

然而,用于GaN功率器件的金刚石衬底、薄膜 或界面在纳米及微米量级,微纳量级厚度的高导热 材料测试一直是业界的技术难点。在该技术方向 的研究基于激光热反射法、谐波法(3ω电学法)、拉 曼光谱法及仿真协同评估的方法实现[11-17]。激光热 反射法包括时域激光热反射(Time-domain thermoreflectance, TDTR) 和频域激光热反射 (Frequency-domain thermoreflectance, FDTR)等方 法,适合用于纳米量级的薄膜和界面热物性的测试 [如图 6(a)所示],其原理是利用激光对样品进行加 热,在皮秒或者纳秒的时间内用探测光对样品表面 的反射率进行测量,利用表面反射率随时间的变化 来获取温度变化趋势从而获取待测材料的热学性 质。该技术优势是时间分辨率高,不仅可以测试薄 膜热导率还可以同时测试其界面热阻。因该技术 仅仅需要在待测材料表面制备薄膜金属电极,制备 工艺相对简单[16-17],目前以美国 DARPA 为主的

GaN器件热管理项目中多采用该测试技术对金刚 石近结集成工艺中的集成界面热阻进行分析,评估 集成工艺的优劣和集成界面传热能力的大小。谐 波热测试方法(3ω电学法)是一种基于交流电加热 与温度振荡耦合关联的测量方法,即在样品上施加 交流电,产生交变焦耳热,导致样品内部温度振荡, 通过分析温度振荡与施加电流频率之间的关系,可 以精确地计算出材料的热导率[14-15],极为适合用于 微纳级薄膜或微米量级厚度的材料热物性的测试 [如图 6(b)、(c)所示]。谐波法表面需要蒸发无限 窄电极作为加热区和信号探测区,制备工艺和条件 相对较高,需要光刻、蒸发或溅射等半导体工艺,因 此,其应用受到较大限制,目前广泛应用于微米量 级厚度金刚石热沉材料的热导率测试,评估各类金 刚石热沉传热能力的大小及其晶圆级金刚石热沉 传热能力的均匀性。

图 6 金刚石及界面热测试方法及原理[12-14]: (a) 时域激光热 反射法;(b)谐波法;(c)厚度适应性

Fig.6 Thermal testing methods and principles for diamond and interface<sup>[12-14]</sup>: (a) Time-domain thermoreflectance; (b) Harmonic method; (c) Thickness adaptability

上述测试技术均是针对材料本身的测试,难以 反映真实金刚石近结集成器件后的传热能力分析, 因此,如何实现金刚石近结集成后的器件内部界面 热阻无损表征已成为行业内重点关注的技术之一。

# GaN器件金刚石近结散热技术

#### GaN器件金刚石衬底键合集成散热技术

金刚石材料作为GaN器件的衬底源于美国

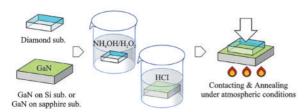

DARPA于2012年牵引NJTT项目。该技术的本质 是首先实现 GaN 功率器件的研制,再将 GaN 器件的 Si或SiC衬底去掉,然后将GaN器件薄膜层与金刚 石衬底进行键合集成,形成自支撑金刚石衬底GaN 功率器件,持续吸引了Systems Land and Armament、Akash Systems、Fujitsu等国际研发机构研发, 目前已经形成以表面活化键合(Surface activated bonding)、亲水键合(Hydrophilic bonding)、原子扩散 键合(Atomic diffusive bonding)等一系列的金刚石衬 底与GaN器件近结集成热管理技术[18-21],目前进展较 好的为表面活化键合技术。该技术是将Si、SiN、 AIN 等介质作为键合层沉积于金刚石表面上,并利 用Ar离子进行活化后,在高真空环境下与GaN器件 进行加压键合,如图7所示,具有代表性的报道为 2022年日本 Device Technology Research Institute 研 究团队在室温下实现金刚石与GaN的表面活化键 合,界面层厚度小至1.5 nm,金刚石/GaN的界面热 阻<10 m2•K/GW[20],但该技术对金刚石和GaN键合 面的粗糙度要求极高(<1 nm)。对于晶圆级键合, 实现高均匀性、低粗糙度的金刚石表面难度很大,与 此同时,在几纳米键合介质的过渡层下,如何实现晶 圆级的键合均匀性和强度也是该技术需要重点突破 的方向。亲水键合技术也是由日本 Device Technology Research Institute研究团队开发,2023年首次报 道了基于亲水键合实现的金刚石与GaN集成,其原 理是通过化学溶液处理在金刚石和GaN键合面生成 OH端,通过在一定压力和温度下的OH端之间反应 实现金刚石与GaN的集成[21],如图8所示,键合层厚 度<5 nm,但该技术OH端反应会产生大量高温水分 子,晶圆级键合过程中难以及时逸出,极大影响键合 效果,是该技术的需要重点解决的难题。

44卷

GaN器件金刚石衬底键合集成散热技术途径 目前依然是先进行GaN器件制备,后进行高导热金 刚石衬底集成。其技术优劣极为明显:优势主要体 现在金刚石衬底可选、GaN器件流片过程中不涉及 金刚石工艺;劣势是键合界面热阻、键合界面均匀 性及键合强度的控制都需系统的技术突破来实现。

GaN/金刚石集成表面活化键合技术[20]

Fig.7 Surface activation bonding technology for GaN/diamond integration[20]

图 8 GaN/金刚石集成亲水键合技术[21]

Fig.8 Hydrophilic bonding technology for GaN/diamond integration<sup>[21]</sup>

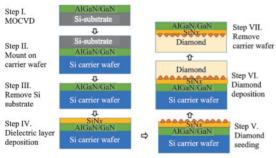

#### 3.2 GaN 器件金刚石衬底生长集成散热技术

GaN器件金刚石衬底生长集成技术也是NJTT 项目主要研究方向之一,由Raytheon、Element Six及 Qorvo牵头,其采用的技术方案是先将GaN外延片 的Si或SiC衬底去除,在GaN背面采用微波等离子 体技术进行金刚石衬底的生长,实现金刚石衬底 GaN 外延片的自支撑制备,最后再基于金刚石衬底 GaN外延片开展GaN功率器件制备,如图9所示[22], 而金刚石衬底GaN外延材料的制备成为该技术途径 的关键。Element Six已成熟制备出金刚石衬底GaN 外延片, 并和 Qorvo 合作制备出金刚石衬底 GaN 功 率器件,其功率密度比传统GaN功率器件提升3.87 倍,但具体的技术路线未见相关文献报道,且国内也 还未见相关金刚石衬底GaN外延片成果的报道,仅 为GaN材料生长金刚石材料的报道。该技术途径需 要在1~2 μm 的 GaN 外延层薄膜上生长高质量金刚 石衬底,还要保证低应力、低翘曲、大尺寸等性能指 标,极大的增加了该技术的难度,但其技术优势也极 为明显,采用生长技术的金刚石衬底GaN外延片的 界面热阻更低,且热阻均匀性更好[22-24]。

图 9 金刚石衬底 GaN 外延晶圆制备技术[22]

Fig.9 Schematic of the main steps for processing a GaN-on-diamond wafer<sup>[22]</sup>

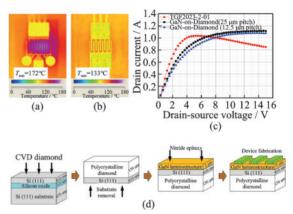

值得关注的是俄罗斯 National Research Center Kurchatov Institute 研究团队提出的新技术方案,即在 (111)晶向的 Si薄膜(厚度 410 nm)表面直接外延生长 金刚石衬底,然后再在 Si薄膜的另一面生长 GaN 外延功能层,实现 Si金刚石衬底的 GaN 外延片,最后进行 GaN 器件流片工艺,制备出 10 栅指、单栅指宽 125 μm 的金刚石衬底 GaN 功率器件。相同结构下进

行对比,金刚石衬底 GaN 器件的结温为 133℃,相比传统同结构 SiC 衬底 GaN 器件(Qorvo 的产品)的结温 172℃,温升下降 39℃,热阻下降 44.8%,在源漏电压为 15 V时,功率提升 37%,如图 10 所示<sup>[23]</sup>。该文章是至今国际上明确金刚石衬底 GaN 外延材料具体制备工艺和器件制备结构的报道,为 GaN 器件金刚石衬底生长集成散热技术提供了新途径参考。

图 10 金刚石衬底 GaN 器件分析<sup>[23]</sup>: (a) SiC 衬底 GaN 器件 散热能力; (b) 金刚石衬底 GaN 器件散热能力; (c) 金 刚石衬底 GaN 器件输出特性; (d) 金刚石衬底 GaN 器 件主要工艺步骤

Fig.10 Analysis of GaN on diamond<sup>[23]</sup>: (a) Heat dissipation capability of GaN on SiC; (b) Heat dissipation capability of GaN on diamond; (c) Output characteristics of GaN on diamond; (d) Schematic of the main steps for processing GaN on diamond wafer

#### 3.3 GaN器件金刚石钝化生长集成散热技术

金刚石钝化散热技术最早由美国 Naval Research Laboratory提出并开展研究,是利用高导热金刚石薄膜替换有源区传统的 SiN 钝化薄膜,使金刚石直接与器件发热区接触,通过金刚石均热作用缓解 GaN 器件的热积累效应。2021年美国 DARPA 持续进行该技术方向的牵引,目前国内外均已取得一定研究成果[25-28]。

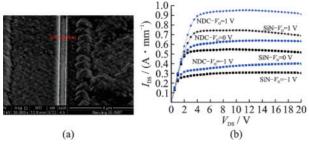

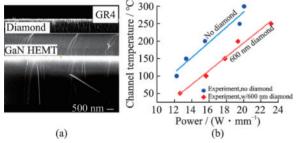

最具有代表性的是 2022年南京电子器件研究所及 2021年斯坦福大学报道的研究工作。南京电子器件研究所团队在国际上率先报道了栅长 < 0.4 µm 金刚石钝化 GaN 功率器件,采用栅前金刚石生长钝化途径,引入多步金刚石微纳刻蚀控制与SiN隔离层创新工艺,研制出金刚石厚度为 500 nm钝化散热结构的 GaN 功率器件,如图 11 所示,相比传统同结构 GaN 器件,热阻下降 21.4%,截止频率基本不变,小信号增益提升 36.7%(10 GHz)<sup>[25]</sup>。斯坦福大学研究团队采用 600 nm 的金刚石钝化层,以5 nm SiN 为隔离缓冲层,制备出单栅指的金刚石钝化结构化 GaN 功率器件,器件结温相比无金刚石钝化结构

的 GaN 器件下降 100~150℃,效果极为明显,但其 GaN 器件的栅结构并未详细给出,仅给出金刚石钝 化生长工艺及其热导率特性,600 nm 厚度的金刚石 钝化层可实现 400 W/(m⋅K)的热导率,是目前报道 的最高水平,如图 12 所示[27]。与此同时,日本 Fujitsu也布局了金刚石钝化GaN器件散热技术,预计可 以实现40%的结温下降能力[6]。

图 11 栅长 0.3 μm 金刚石钝化 GaN 器件及输出特性[25]: (a) 栅长; (b) 输出特性

Fig.11 Structure and output characteristics of diamond passivated GaN device with gate length of 0.3 µm<sup>[25]</sup>: (a) Gate length; (b) Output characteristics

图 12 金刚石钝化 GaN 器件结构与散热能力[27]: (a) 金刚石 钝化结构;(b)散热能力

Fig.12 Structure and heat dissipation capability of diamond passivated GaN device<sup>[27]</sup>: (a) Structure of diamond passivated; (b) Dissipation capability

GaN器件金刚石钝化生长集成散热技术的重 点是实现高热导率金刚石钝化薄膜的制备及其与 GaN器件流片工艺兼容性。其技术优劣极为明显: 优势主要体现在金刚石薄膜仅作为GaN器件钝化 层,替换原有的SiN钝化层,工艺兼容性强,相对散 热能力的经济性价比高;劣势是金刚石钝化层热导 率、钝化层应力及其金刚石的高精度刻蚀都需要系 统的技术突破来实现。

#### 4 结束语

针对GaN器件大功率及高功率密度潜能受限 于热积累效应,难以满足新一代信息化系统小型 化、多功能化发展的需求问题,系统的进行了GaN 器件金刚石近结集成散热技术能力、技术评估方法 及工艺开发途径的分析。因器件自身结构和材料

热物性限制,热积累严重影响 GaN 器件大功率应用 及可靠性。以美国DARPA近结热管理计划为牵 引,详细分析了GaN器件金刚石近结集成热管理技 术的各类研究方法及面临的技术挑战。在金刚石 近结集成热设计及工艺传热能力评估方面,实现了 热设计、界面热阻及金刚石热沉的评估技术,但金 刚石近结集成GaN器件的多层级材料结构、材料热 物性等多种因素耦合影响机制及其影响规律的定 量评估还缺乏系统的研究,且金刚石近结集成后的 器件内部界面质量的无损评估技术还有待进一步 提升。GaN器件金刚石衬底键合集成散热技术具 有金刚石热导率可控且对GaN器件性能影响较小 的技术优势,已成为国内外研究重点,但键合界面 热阻、键合界面均匀性及其键合强度的控制都需要 系统的技术突破来进一步实现。GaN器件金刚石 衬底生长集成散热技术需要在≤2 μm 厚的 GaN 外 延层薄膜上生长高质量、低应力、低热阻、低翘曲和 大尺寸的金刚石热沉,极大地增加了该技术的难 度,目前仅俄罗斯研究团队公开了详细的技术方 案,并实现了金刚石衬底GaN器件的研制。GaN器 件金刚石钝化生长集成散热技术优势是金刚石薄 膜仅作为GaN器件钝化层,工艺兼容性强,散热能 力经济性价比高,但金刚石低温钝化质量控制及其 与GaN器件工艺兼容性还需要系统的技术突破来 实现。GaN功率器件金刚石近结集成散热技术具 有极大的创新型和颠覆性,也代表了电子器件的热 管理由封装级正式迈入芯片级,引领了散热技术、 热表征技术向微纳量级研究发展,已成为解决未来 高功率密度器件热积累瓶颈的重要发展方向。

44卷

#### 文 献

- [1] Lu M C. Development of diamond device-level heat spreader for the advancement of GaN HEMT power and RF electronics [J]. IEEE Transactions on Device and Materials Reliability, 2023, 23(4): 468-485.

- [2] Zhou X, Malakoutian M, Soman R, et al. Impact of diamond passivation on  $f_T$  and  $f_{max}$  of mm-wave N-polar GaN HEMTs[J]. IEEE Transactions on Electron Devices, 2022, 69(12): 6650-6655.

- [3] Jaman I A, Karim T, Rahman M A, et al. Temperature response and power dissipation in GaN HEMT on diamond substrate [C]. 2024 6th International Conference on Electrical Engineering and Information & Communication Technology (ICEEICT). Dhaka, Bangladesh: IEEE, 2024: 533-537.

- [4] Francis D, Kuball M. GaN-on-diamond materials and device technology: a review[J]. Thermal Management of Gallium Nitride Electronics, 2022, 14: 295-331.

- [5] Field DE, Beale R, Getzler N, et al. Evaluating the interfacial toughness of GaN-on-diamond with an im-

- proved analysis using nanoindentation[J]. Scripta Materialia, 2022, 209: 114370.

- [6] Ma G, Wang Y, Xia R, et al. Modulating microstructure and thermal properties of diamond/SiN<sub>x</sub>/GaN multilayer structure by diamond growth temperature[J]. Diamond and Related Materials, 2024, 141: 110717.

- [7] Guggenheim R, Rodes L. Roadmap review for cooling high-power GaN HEMT devices [C]. 2017 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS). Tel-Aviv, Israel: IEEE, 2017: 1-6.

- [8] Microsystems Technology Office. Technologies for Heat Removal in Electronics at the Device Scale (THREADS): HR001123S0013[EB/OL]. (2022-11-18)[2024-10-09]. https://sam.gov/opp/efe061b616704f59a798c9d72163e678/view.

- [9] Guo H X, Kong Y C, Chen T S. Thermal simulation of high power GaN-on-diamond substrates for HEMT applications[J]. Diamond and Related Materials, 2017, 73: 260-266.

- [10] Kim T, Song C, Park S I, et al. Modeling and analyzing near-junction thermal transport in high-heat-flux GaN devices heterogeneously integrated with diamond [J]. International Communications in Heat and Mass Transfer, 2023, 143: 106682.

- [11] Yussof A M M, Abdullah M F, Ridzwan M N A M, et al. Revisiting the effectiveness of diamond heat spreaders on multi-finger gate GaN HEMT using chipto-package-level thermal simulation [J]. Microelectronics Reliability, 2024, 161: 115496.

- [12] Altman D, Tyhach M, McClymonds J, et al. Analysis and characterization of thermal transport in GaN HEMTs on diamond substrates [C]. Fourteenth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm). Orlando, FL, USA: IEEE, 2014: 1199-1205.

- [13] Yan Z, Julian A, James P, et al. Barrier-layer optimization for enhanced GaN-on-diamond device cooling [J]. ACS Applied Materials & Interfaces, 2017, 9 (39): 34416-34422.

- [14] Dames C. Measuring the thermal conductivity of thin films: 3 omega and related electrothermal methods [J]. Annual Review of Heat Transfer, 2013, 16: 7-49.

- [15] Yang G, Cao B Y. Three-sensor 3ω-2ω method for the simultaneous measurement of thermal conductivity and thermal boundary resistance in film-on-substrate heterostructures [J]. Journal of Applied Physics, 2023, 133 (4): 045104.

- [16] Cheng Z, Mu F W, Ji X Y, et al. Thermal visualization of buried interfaces enabled by ratio signal and steady-state heating of time-domain thermoreflectance [J]. ACS Applied Materials & Interfaces, 2021, 13 (27): 31843-31851.

- [17] Ren W J, Lu S, Yu C Q, et al. Impact of moiré superlattice on atomic stress and thermal transport in van der Waals heterostructures [J]. Applied Physics Reviews, 2023, 10(4): 041404.

- [18] Liang JB, Masuya S, Kasu M, et al. Realization of direct bonding of single crystal diamond and Si substrates [J]. Applied Physics Letters, 2017, 110(11): 111603.

- [19] Matsumae T, Kurashima Y, Takagi H, et al. Room temperature bonding of GaN and diamond substrates via atomic layer[J]. Scripta Materialia, 2022, 215: 114725.

- [20] Matsumae T, Kurashima Y, Takagi H, et al. Room temperature bonding of GaN and diamond substrates via atomic layer[J]. Scripta Materialia, 2022, 215: 114725.

- [21] Matsumae T, Okita S, Fukumoto S, et al. Simple low-temperature GaN/diamond bonding process with an atomically thin intermediate layer [J]. ACS Applied Nano Materials, 2023, 6(15): 14076-14082.

- [22] Liu D, Fabes S, Li B S, et al. On the characterisation of the interfacial toughness in a novel "GaN-on-Diamond" material for high-power RF devices [J]. ACS Applied Electronic Materials, 2019, 1(3): 354-369.

- [23] Chernykh M Y, Andreev A A, Ezubchenko I S, et al. GaN-based heterostructures with CVD diamond heat sinks: a new fabrication approach towards efficient electronic devices[J]. Applied Materials Today, 2022, 26: 101338.

- [24] Sandhu R, Gambin V, Poust B, et al. Diamond materials for GaN HEMT near junction heat removal [C].

2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS). La Jolla, CA, USA:

IEEE, 2012: 1-1.

- [25] Guo H X, Li Y Z, Yu X X, et al. Thermal performance improvement of AlGaN/GaN HEMTs using nanocrystalline diamond capping layers [J]. Micromachines, 2022, 13(9): 1486.

- [26] Arivazhagan L, Nirmal D, Reddy P K, et al. A numerical investigation of heat suppression in HEMT for power electronics application[J]. Silicon, 2021, 13: 3039-3046.

- [27] Malakoutian M, Ren C H, Woo K, et al. Development of polycrystalline diamond compatible with the latest N-polar GaN mm-wave technology [J]. Cryst Growth Des, 2021, 21: 2624-2632.

- [28] Malakoutian M, Laurent M A, Chowdhury S, et al. A study on the growth window of polycrystalline diamond on Si<sub>3</sub>N<sub>4</sub>-coated N-polar GaN[J]. Crystals, 2019, 9: 498.

郭怀新(GUO Huaixin) 男,1984年生, 黑龙江齐齐哈尔人,博士,正高级工程 师,主要研究方向为器件级热管理。