**DOI:**10.12450/j.gtdzx.202404015

# 浮栅和高压栅极共掺在EEPROM中的应用研究

刘冬华\* 陈云骢 钱文生

(上海华虹宏力半导体制造有限公司,上海,201206) 2024-04-01 收稿,2024-05-28 收改稿

摘要:为简化电可擦除可编程只读存储器(Electrically-erasable programmable read-only memory, EEPROM)的制造工艺以及减少等离子体对隧道氧化层的损害,重点分析了将浮栅多晶硅和高压器件的栅极共同掺杂对存储器件和高压器件的影响,包括不同掺杂浓度下 EEPROM 存储单元的擦写速度、读取电流、可靠性以及高压晶体管的电学特性等相关分析,探讨优良器件特性的最优掺杂浓度设计方法,为器件性能优化以及工艺改进提供参考。

关键词:EEPROM;浮栅;共掺

中图分类号: TN4; TM74 文献标识码: A 文章编号: 1000-3819(2024)04-0363-04

## Research on the Application of Floating Gate and High-voltage Gate Co-doping in EEPROM

LIU Donghua CHEN Yuncong QIAN Wensheng

(Shanghai Huahong Grace Semiconductor Manufacturing Corporation, Shanghai, 201206, CHN)

**Abstract:** Based on the perspective of simplifying the process of electrically-erasable programmable read-only memory (EEPROM) manufacturing and reducing the damage of plasma to the oxide layer of the tunnel, this paper focused on the analysis of the effects of the co-doping of the gate of the floating gate polysilicon and the high-voltage device on the memory device and the high-voltage device, including the analysis of the erasing speed, read current, reliability and electrical characteristics of high-voltage transistor of the EEPROM memory cell under different doping concentrations. This paper discussed the optimal doping concentration design method for obtaining better device characteristic, which provided an important theoretical basis for device optimization and process improvement.

Key words: EEPROM; floating gate; co-doping

### 引言

电可擦除可编程只读存储器(Electrically-erasable programmable read-only memory, EEPROM)作为非挥发性半导体存储器的一种,自20世纪70年代末以来越来越受到人们的重视[1-3]。它具有工作速度快、字节擦除和编程,使用灵活、可靠性好等优点,可以方便有效地在系统中进行数据的存储和刷

新<sup>[4]</sup>。在不同结构类型的EEPROM中,浮栅隧道氧化层结构的EEPROM相对其他结构工艺更简单,耐久性和保持性更加理想,并且与CMOS工艺兼容,因此获得了广泛地应用,成为非挥发性存储器的重要组成部分<sup>[5]</sup>。

采用浮栅型技术存储数据的 EEPROM,在 10 MV•cm<sup>-1</sup>以上的场强下要使隧道窗口发生F-N 隧穿(Fowler-Nordheim tunneling)效应,需要在 EE-PROM 单元上施加超过 13 V 的电压。较高的工作

电压使得相对普通的 CMOS 工艺而言, EEPROM 部分的制造技术更为复杂。因此如何降低 EE-PROM 工艺复杂度,是目前业界一直关注的重点。 此外,提高 EEPROM 的擦写性能也是业界的重点 研究方向。要获得快速擦写就需要更薄的隧道氧 化层,相应的工艺难度更大,与此相对应的等离子 体对氧化层的损害将成为不可忽视的重要失效因 素[6-7]。等离子体损伤(Plasma damage)产生的机理 是:在工艺过程中,由于等离子体密度、电子温度或 离子束流的设备中电荷中和的不均,导致离子和电 子通量的不平衡,并最终导致形成大面积的硅片上 电极和硅片间的电势不均。工艺中的等离子体损 伤在电极完全暴露的工序中尤其明显,比如工艺制 造过程中的去胶和杂质离子注入就是典型的与硅 片表面充电差异相关的工序,这种工序往往有较高 几率带来大量的离子损失[8]。

在传统的 EEPROM 存储模块制造工艺中,为降低高压晶体管的栅极电阻,同时保持 EEPROM 单元浮栅的掺杂浓度,需要额外增加一道光刻工序对高压晶体管的栅极进行重掺杂然后再去掉增加的光刻胶。这个额外的工序不仅使制造过程工艺成本提高,而且由于此时存储单元的隧道氧化层已经形成,额外的去胶工序对应的等离子体也会对隧道氧化层造成严重的损害。

为降低 EEPROM 制造过程中的工艺成本、提高 EEPROM 存储器单元的可靠性,本文从减少工艺制造过程中的去胶和杂质离子注入的角度出发,重点分析将浮栅和高压器件管栅极合并掺杂对 EEPROM 存储单元和高压器件的影响。

#### 1 实 验

传统工艺中,EEPROM器件和高压器件的栅极分开进行掺杂,要用到两次光刻和离子注入,并且它们的注入条件有差异。本文将EEPROM器件和高压器件的栅极合并掺杂,只需要一道光刻,并采用相同的注入条件。为了评估合并掺杂之后器件特性的变化,首先采用半导体工艺与器件的模拟软件Sentaurus仿真了在不同掺杂条件下三种高压器件阈值电压(V<sub>th</sub>)的变化,三种高压器件包括18 V NMOS、18 V PMOS的外围高压晶体管及14 V NMOS存储单元的选择管,然后采用安捷伦的半导体特性分析仪(型号为HP4156C)分别测试不同掺杂浓度对EEPROM存储单元的擦写速度、

读取电流、可靠性以及高压晶体管的电学特性的 影响。

### 2 结果与讨论

#### 2.1 高压晶体管的电学特性

http://gtdzx.cetc55.com

表 1 为三种高压晶体管在不同栅极掺杂浓度下的阈值电压模拟结果。栅极中分两次分别注入了砷 (As)和磷 (Ph)杂质,其中浓度更高的磷是主掺杂。砷的掺杂浓度为  $5 \times 10^{14}$  cm $^{-2}$ ,注入能量为 50 keV;磷有四种掺杂浓度,分别是  $3 \times 10^{15}$ 、 $2 \times 10^{15}$ 、 $1 \times 10^{15}$  和 0 cm $^{-2}$ (无注入),注入能量均为 50 keV。本文以实验 1 掺杂条件 (Ph 掺杂浓度为  $3 \times 10^{15}$  cm $^{-2}$ )下的器件电学特性为基准,然后依次降低栅极掺杂浓度,模拟 EEPROM 存储单元浮栅掺杂浓度对高压器件的电学特性影响情况。从模拟结果可以看到,随栅极掺杂浓度降低高压器件的  $V_{th}$ 变化相对较小(最大的  $V_{th}$ 变化在 50 mV 左右)。当磷掺杂剂量为  $1 \times 10^{15}$   $\sim 3 \times 10^{15}$  cm $^{-2}$ 时,高压器件的  $V_{th}$ 变化范围在 2% 以内。

# 表 1 三种高压晶体管在不同栅极掺杂剂量下的阈值电压 模拟结果

Tab.1 Simulated results of threshold voltage for three types of high-voltage transistors under different gate doping doses

| Parm.  | Dose(As)<br>/cm <sup>-2</sup> | Dose(Ph)<br>/cm <sup>-2</sup> | $V_{ m th(18~V~NMOS)} / { m V}$ | $V_{ m th(14~V~NMOS)} / { m V}$ | $V_{ m th(18~V~PMOS)} / V$ |

|--------|-------------------------------|-------------------------------|---------------------------------|---------------------------------|----------------------------|

| Test 1 | 5×10 <sup>14</sup>            | $3 \times 10^{15}$            | 0.650                           | 1.000                           | -0.910                     |

| Test 2 |                               | $2 \times 10^{15}$            | 0.651                           | 1.005                           | -0.907                     |

| Test 3 |                               | $1 \times 10^{15}$            | 0.654                           | 1.020                           | -0.890                     |

| Test 4 |                               | 0                             | 0.669                           | 1.050                           | -0.856                     |

#### 2.2 EEPROM存储单元的相关特性

#### 2.2.1 擦写特性

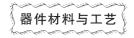

图 1(a)和(b)分别是 EEPROM 器件的结构示意图和等效电路。作为 EEPROM 器件关键技术之一的隧道窗口设计,本文 EEPROM单元选取了 8 nm 隧穿氧化层,隧道窗口(Tunnel window, TW)的面积设计为  $0.27 \, \mu m \times 0.27 \, \mu m$ 。编程和读取条件分别为:编程电压( $V_{PP}$ )为  $13 \, V$ ;读取时位线(Bit line, BL)施加  $1 \, V$  电压,字线(Word line, WL)则是  $5 \, V$  的电源电压( $V_{DD}$ )。 EEPROM 存储单元在数据擦除、编程写人和读取电流时的电压偏置如表  $2 \, \text{所示}$ ,

其编程与擦除方式均是F-N隧穿。

- 图 1 EEPROM 器件: (a) 结构示意图; (b) 等效电路; (c) 浮 栅掺杂浓度变化对电荷隧穿势垒的影响示意图

- Fig.1 EEPROM device: (a) Cross-section diagram of the structure; (b) Equivalent circuit; (c) Schematic diagram of the effect of floating gate doping concentration variation on charge tunneling barrier

#### 表 2 EEPROM 存储单元在数据擦除、编程写入和读取电 流时的电压偏置

Tab.2 Voltage bias of EEPROM storage unit during data erasure, programming writing and current reading

| Bias voltage | Erase "0"                         | Write "1"                         | Read                           |

|--------------|-----------------------------------|-----------------------------------|--------------------------------|

| Bit line     | 0                                 | $V_{\scriptscriptstyle 	ext{PP}}$ | 1 V                            |

| Word line    | $V_{\scriptscriptstyle 	ext{PP}}$ | $V_{\scriptscriptstyle	ext{PP}}$  | $V_{\scriptscriptstyle  m DD}$ |

| Control gate | $V_{\scriptscriptstyle 	ext{PP}}$ | 0                                 | 0                              |

此 EEPROM 单元的编程过程是: 当位线加  $V_{\rm PP}$  高压,高压通过选择管开启传输到 EEPROM 单元的漏端,产生一个足够高的电场,从而使得电子可以克服能量势垒从浮栅(Floating gate, FG)经过隧穿氧化层进入漏端,完成写入过程;擦除过程是 EEPROM 单元的控栅(Control gate, CG)加上高压,电子从漏端隧穿进浮栅多晶硅,即编程过程电子离开浮栅,擦写过程电子进入浮栅。当一高电压加在多晶硅控栅(电压通过耦合传到浮栅)一二氧化硅隧道氧化层一隧道下的硅结构上,该结构的能带就会发生变化,浮栅和硅之间的势垒差被改变,如能带示意图 1(c)所示。势垒高度  $\Delta V$  由浮栅多晶硅和硅的能带结构决定,在写入过程中,电子从浮栅隧穿至硅需要克服  $\Delta V$  的能量势垒,当浮栅掺杂浓度增大时,浮栅与硅的导带之间的能量差增大至  $\Delta V_1$ ,相

应的电子能量势垒  $\Delta V_i > \Delta V$ ,因此编程时,浮栅掺杂浓度增大,电子隧穿必须克服的势垒增大,相应地选择管传输的高压要消耗更大的能量去克服此能量势垒,编程时间延长。所以为了实现相同的编程效果(比如使相同数量的电子发生跃迁),要么增加编程电压  $V_{PP}$ ,要么增加编程的时间。相反,擦除时电子从硅进入浮栅,浮栅与硅之间的存在的能量势垒差使施加在控栅上的高压增大。因此,浮栅掺杂浓度越大,擦除时所得的电压越大,所需时间越短。

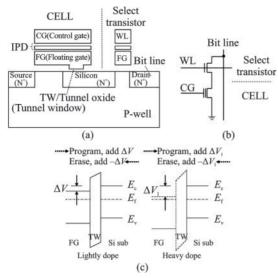

图 2是 EEPROM 单元在四种不同浮栅掺杂浓度下的擦写特性曲线,其中  $I_{\rm E}$ 表示擦除操作后的读取电流。从图中可以看到,随着浮栅掺杂浓度的增大,存储单元的编程速度减慢,擦除所需时间减短。参考条件  $[I_{\rm E}({\rm ref}) \setminus I_{\rm w}({\rm ref})]$ 下的性能介于5个实验结果的中间,用于对比(为一组合实验条件的结果,包括栅极掺杂剂量实验)。因为擦除时电子的运动方向与编程时相反,电子是从高能级的P型硅跃迁到低能级的N型浮栅,势垒差变大,有助于跃迁,因此保持外部加载的擦除电压不变时,达到相同擦除效果所需的时间变短。

图 2 不同浮栅掺杂浓度下存储单元的擦写特性曲线 Fig. 2 Characteristic curves of storage cells under different floating gate doping concentrations

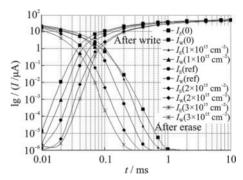

而针对目前业界 EEPROM 毫秒级的擦写速度标准,四种不同掺杂浓度的 EEPROM 单元都能满足。此外,读取电流大小也是衡量 EEPROM 存储单元的性能参数之一。图 3 中纵轴取线性坐标,清楚地显示了写人后的读取电流随浮栅掺杂浓度的增大而减小。当掺杂剂量大于 $1\times10^{15}$  cm $^{-2}$ ,编程擦写时间为 2 ms 时,电流略低于设计目标电流值(40  $\mu$ A)。综合考虑高压晶体管的性能、EEPROM的编程和擦除电压与时间, $1\times10^{15}$  cm $^{-2}$ 磷剂量的掺杂较优。

固体电子学研究与进展

图 3 不同浮栅掺杂条件下存储单元的读取电流随写入时 间的变化曲线

Fig.3 The variation curves of read current of storage cells with writing time under different floating gate doping conditions

#### 2.2.2 可靠性

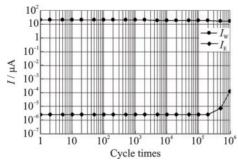

EEPROM存储器单元中影响器件可靠性的关 键在于隧穿氧化层(Tunnel oxide)和栅层间介质 (Inter poly-gate dielectric, IPD)的质量。浮栅多晶 硅掺杂的工艺变化对隧穿氧化层和IPD可能存在 影响,因此浮栅掺杂浓度变化后 EEPROM 存储单 元的可靠性评价必不可少。本文选取对于高压晶 体管和存储单元特性变化最优的合并掺杂条件 (1×10<sup>15</sup> cm<sup>-2</sup>磷剂量)进行存储单元耐久性测试,测 试方法是对单个存储单元不断进行擦除编程,循环 次数 100 万次,记录单元编程擦除完成后电流的变 化情况。测试条件为室温,电源电压 $V_{DD}$ 为5 $V,V_{PP}$ 电压13.4 V,编程擦写时间为2.5 ms。测试结果如 图 4 所示,存储单元满足可编程电路擦写循环次数 100万次的要求。对于数据保持性,本文采取对内 含1kB容量的EEPROM进行全芯片编程,再进行 250℃、24 h的烘烤,烘烤后读取 EEPROM 的电流, 其失效率在1%以内,表明单元的数据保持性较 理想。

图 4 磷掺杂剂量为  $1 \times 10^{15} \, \mathrm{cm}^{-2}$ 的存储单元的耐久性测试 电流随循环周期变化曲线

Fig.4 The durability test current curves of a storage unit with a phosphorus doping dose of  $1\times10^{15}~\mathrm{cm}^{-2}$  as a function of the cycle times

#### 结 3 论

通过对浮栅隧道氧化层结构 EEPROM 单元技 术的研究,从工艺改进和减少等离子体对隧道氧化 层的损害的角度,设计分析了将浮栅多晶硅和高压 器件的栅极共同掺杂的工艺技术,并详细评估了不 同掺杂浓度下EEPROM存储单元的擦写速度、读 取电流、存储单元的可靠性以及高压晶体管的电学 特性等器件相关信息:探讨了对器件特性影响较小 的最优掺杂浓度,达到了实际应用要求。

#### 考文献

- [1] 李海鸥,刘耀隆,朱蒙洁,等,应用于低频无源RFID 的低成本 2 kbit EEPROM[J]. 微电子学, 2023, 53 (2): 261-266.

- [2] 闫娜, 谈熙, 赵涤燹, 等. 一种适用于射频电子标签的 超低功耗嵌入式 EEPROM[J]. 半导体学报, 2006, 27 (6):994-998.

- [3] Hu J G, Wang D M, Wu J. A 2 kbits low power EE-PROM for passive RFID tag IC[J]. Chinese Journal of Electronics, 2022, 31(1): 18-24.

- [4] 石永慧. EEPROM 存储数据耗时问题探究分析[J]. 山 西电子技术, 2023(4): 93-96.

- [5] 葛优, 邹望辉. 基于常规 CMOS 工艺的单层多晶硅 EEPROM 单元设计[J]. 电子元件与材料, 2022, 41 (7): 719-724.

- [6] 赵扬, 陈燕宁, 单书珊, 等. 基于栅氧化层损伤 EEPROM 的失效分析[J]. 半导体技术, 2020, 45(1): 72-76.

- [7] 刘之景, 刘晨. 等离子体充电损伤对氧化门厚度的依 赖关系[J]. 仪表技术与传感器, 2000(3): 8-10, 37.

- [8] 朱志炜,郝跃,赵天绪,等.等离子体工艺引起的 MOSFET 栅氧化层损伤[J]. 固体电子学研究与进 展,2003(1):126-132.

刘冬华(LIU Donghua) 男,1974年12 月生,江西赣州市人,2018年获复旦大学 工学博士学位,高级工程师,技术专长为 半导体工艺和器件设计,研究方向包括 式存储器、高速异质结器件和功率器件, 目前担任上海华虹宏力半导体制造有限 公司器件设计部部门长。

钱文生(QIAN Wensheng) 男,1968年7月生,安徽铜陵市 人,1996年获东南大学微电子中心工学博士学位,教授级高 工,长期从事先进器件的设计工作,目前担任上海华虹宏力 半导体制造有限公司器件与设计中心副总裁。