微电子与微系统

**DOI:**10.12450/j.gtdzx.202404011

## 基于电路模拟的集成电路失效机理研究

龚瑜,

(深圳赛意法微电子有限公司,广东,深圳,518038) 2023-11-08收稿,2024-01-17收改稿

摘要:随着集成电路结构和电路复杂性的增加,故障源头的判定和失效根本原因的分析也越来越困难。目前集成电路的失效分析研究主要集中在利用先进的分析仪器搜集证据进而推导失效机理,缺乏对失效的模拟反向验证。本文针对集成电路故障进行失效分析,检测到具体的物理损伤点,利用 Multisim 的工具,依据物理损伤位置和特征建立相应物理模型,研究缺陷对故障结果的贡献,进而确定故障的真正源头,同时与实际样品的测试结果进行对比验证,复现了集成电路的失效机理和失效过程。

关键词:故障仿真;电路模拟;失效分析;失效机理;仿真软件

中图分类号:TN407 文献标识码:A 文章编号:1000-3819(2024)04-0337-06

# Study on the Circuit Simulation Technology on Integrated Circuit Failure Mechanism Analysis

GONG Yu

(STS Microelectronics Co., Ltd., Shenzhen, Guangdong, 518038, CHN)

**Abstract:** As the complexity of integrated circuit structures and circuits increases, to verify the source of failure and the real root cause of failure become more and more difficult. However, at present, the failure analysis research of integrated circuits mainly focuses on the use of advanced analytical instruments to collect evidence and derive the failure mechanism but lacks the simulation and reverse verification of failure. In this paper, the failure analysis is carried out to detect the specific physical damage points for the integrated circuit fault, and the corresponding physical model is established according to the location and characteristics of the physical damage by using the Multisim tool, and the contribution of the defect to the fault result is studied, and then the real source of the fault is determined, and the failure mechanism and failure process of the integrated circuit are reproduced by comparing the test results with the actual sample.

Key words: fault emulation; circuit simulation; failure analysis; failure mechanism; simulation software

引言

随着集成电路产业的发展,集成电路在栅极尺寸<sup>[1]</sup>、第三代半导体领域<sup>[2]</sup>以及3D结构方面<sup>[3]</sup>取得

了巨大进展。然而,随着集成电路的特征尺寸的不断降低,集成电路内部的缺陷大小也在不断减小;同时,随着集成电路内部晶体管增多,功能越来越复杂,内部缺陷的相互关联性越来越复杂,因此,集成电路的失效分析的难度也在不断增加。加之集

成电路的应用场景越来越恶劣,给现在的失效分析 带来了很大的挑战。

固体电子学研究与进展

失效分析的结论是基于失效分析过程中所收 集的信息进行的最具可能性的推断。在集成电路 失效分析过程中所检测到的物理损伤点可能并非 是真正失效的原因,这是因为引发失效的根本缺陷 位置可能无法被微光显微镜(Emission microscope, EMMI)、光诱导电阻变化(Optical beam induced resistance change, OBIRCH)、红外热成像技术(Infrared thermal imager)等失效定位仪器所表征[4],或者 被激发的关联电路的物理缺陷信号掩盖了真实的 物理缺陷。虽然借助电路原理图和版图进行故障 假设和分析[5]可以从正向完成失效模式的推断,但 是无法进行失效的模拟和验证,形成闭环。因此, 对物理缺陷点进行模拟验证就极为重要。但目前 行业对集成电路特定电路的缺陷失效模拟与验证 方面的研究比较少。

Multisim 是艾默生公司推出的以 SPICE 为基 础的仿真工具[6-7]。这个工具提供了在不同偏置条 件下的集成电路电流电压波形的分析功能,能够有 效地针对集成电路特定模块的特定故障进行模拟 分析。本文针对存在故障的集成电路进行故障检 测,使用失效分析技术检测到具体的物理损伤点, 然后利用 Multisim 工具,依据物理损伤位置和特征 建立相应故障物理模型,研究缺陷对故障结果的贡 献,进而确定故障的真正起点,同时与实际样品的 测试结果进行对比验证,复现了集成电路的失效机 理和失效过程,这对失效机理的探究和失效起源的 分析具有重要意义。

#### 1 原理与方法

## 1.1 基于电路仿真的失效模拟流程

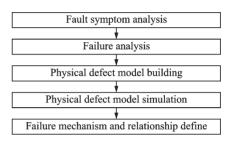

图 1 是应用电路仿真软件进行集成电路失效模 拟分析的流程图。该流程包括了以下步骤:

- (1)集成电路故障模式分析。包括测量集成电 路的电气性能,研究失效的参数,失效的输出性能。

- (2)失效分析检测物理损伤点。包括外观检 测、电性能测试、X射线检测、超声波扫描分析、化学 开封、背部开封研磨技术、离子束切割等失效分析 手段,收集所有的物理缺陷点。

- (3)物理缺陷点模型建立。建立集成电路物理 缺陷点的失效模型,带入相关电路。研究失效缺陷

对相关电路电压、电流等参数的影响。与真实的测 量参数进行比对,计算出模型的数值。

- (4)物理缺陷模型仿真分析。将建立的模型代 入相关电路,分析对集成电路功能的影响,与实际 测量的输出结果进行比对,验证缺陷与最终芯片输 出的关联性。

- (5)确定最终的失效机理和失效联系。

图 1 失效模拟和故障仿真的流程图

Fig.1 Flow chart of failure simulation and fault emulation

## 1.2 故障模型

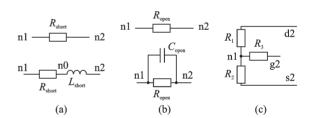

不同的缺陷形式可以根据电路的需要选择不 同的故障模型,如图2所示。在硬性失效中,可以选 择加入三极管、二极管;而在参数失效的案例中,可 以选择在电路中加入电阻、电容、电感等。

图 2 失效模型案例: (a) 短路; (b) 开路; (c) 栅极开路

Fig.2 Examples of fault model: (a) Short-circuit; (b) Opencircuit; (c) Gate-open

## 失效案例

本文所研究的产品为一款商用电流模式主级 控制器芯片。产品内置了准谐振功能模块,它能够 感应到主电路的输入电压异常变化进而对驱动金 属氧化物半导体场效晶体管(Metal-oxide-semiconductor field-effect transistor, MOSFET)进行及时关 断,以避免转换频率过高引发器件失效。

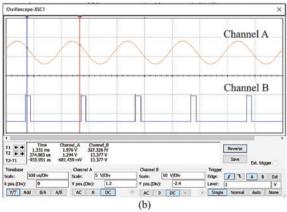

### 2.1 故障现象

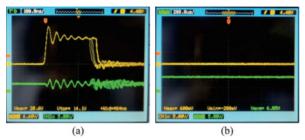

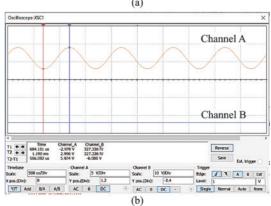

为研究同批次检测到的5粒栅极驱动输出异常 的故障品,使用示波器 Keysight DSO1024A 进行正 常品和故障品的输出波形检测,输出结果如图3所 示。其中黄色曲线为栅极驱动输出波形,绿色曲线为总线反馈电压(Voltage feed forward, VFF)波形。

如图 3(a) 所示, 正常品能够进入准谐振模式: 当 VFF 超过 3.1 V时, 栅极驱动输出会被正常打开, VFF 电压的最高值能达到 6 V。相反, 5 粒故障品出现了相同的失效现象: 当 VFF 上的电压超过3.1 V时,产品在第1秒进入谐振模式; 随后, 栅极驱动上的电压迅速升高至 15 V, 最终降低到 0 V [如图 3(b) 所示]。

图 3 总线反馈电压变化时栅极驱动输出电压的即时波形: (a) 正常品进入打嗝模式;(b) 故障品输出异常

Fig.3 The time dependence of the gate driver output voltage for VFF change: (a) Good reference sample enter to hip-hop mode; (b) Failed sample output abnormal

## 2.2 失效分析

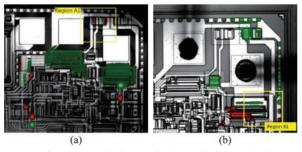

对故障品进行全流程失效分析。首先进行非破坏性分析,包括光学显微镜检查、X射线检查、超声扫描等,未发现异常。然后使用曲线追踪仪测量产品零电流检测端(Zero current detector, ZCD)与地端管脚间的 I-V 曲线,故障品与正常品之间有微小差异。根据电性能测试结果进行样品制备,裸露内部集成电路,使用搭载了微光显微镜和光诱导电阻变化系统的 HAMAMATSU IPHEMOS-MP 机型完成失效定位,发现两处异常点(Region A1, Region B1),如图4所示。

图 4 光诱导电阻变化检测异常点: (a) 故障品正向偏压; (b) 故障品反向偏压

Fig.4 Abnormal points observed by OBIRCH: (a) Failed sample with positive bias; (b) Failed sample with negative bias

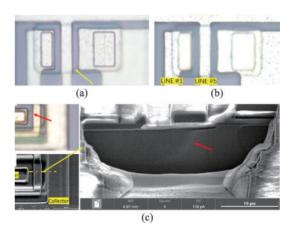

对异常点位置进行芯片逐层去层分析以及聚焦离子束(Focused ion beam, FIB)截面切割和阱染色分析,最终在集成电路上检测到两处物理缺陷点,如图5所示。

物理缺陷1是结掺杂异常点,在图4(a)所示Region A1位置,图5(a)为故障品,图5(b)为正常样品。从电学性能上来看,结掺杂的差异会影响区域二极管的电阻值,因为N型掺杂阱区域(N-well)的片电阻值远远大于P型体电阻(P-body)的数值。这个异常影响到VFF相关参数,进而影响到最终的产品输出性能。图5(c)为检测到的物理缺陷2,位于图4(b)所示Region B1位置,高倍显微镜下发现异常,经过FIB截面切割和截面阱染色分析,检测到异常的掺杂缺陷,故障品的结掺杂范围明显高于正常品,这导致了基级(Base)和集电极(Collector)之间的导通电阻增大。与ZCD端点结果一致,也可能会影响到最终的产品输出性能。

图 5 物理缺陷点: (a) 光学显微镜下故障品缺陷1位置的图片; (b) 光学显微镜下正常品缺陷1位置的图片; (c) 故障品的聚焦离子束切割截面缺陷2位置的图片

Fig.5 The observed physical defects: (a) Failed sample defect 1 optical microscope picture; (b) Good reference sample defect 1 optical microscope picture; (c) FIB cut on the failed sample defect 2

## 3 故障仿真分析

对失效产品的分析结果显示,故障品内部电路中存在两种物理缺陷(物理缺陷1、2),利用 Multisim 进行故障仿真,研究物理缺陷对最终输出的影响。使用示波器 Keysight MSOS254A 进行产品的栅极驱动输出波形检测。

## 3.1 相关失效电路

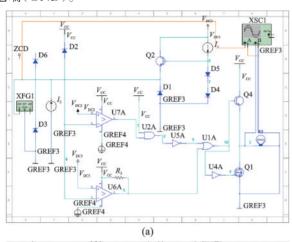

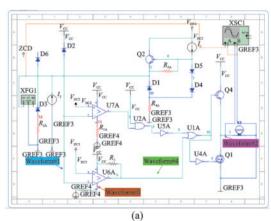

实验样品的失效相关电路如图 6(a) 所示,其中

不相关的电路部分已经进行简化,相关电路承担着 主线电路电压监测的功能,如图 6(b)、(c)所示。当 ZCD 感应到的电压低于 0.2 V 时, 芯片会立即自动 关断;当芯片监测到从2.1V到0.2V的下降沿电压 时,芯片进入过流保护工作模式,这时栅极驱动 (Gate driver, GD)输出端输出测量数值为0V,且 实测结果与仿真基本吻合; 当感应电压高于 2.2 V 时,芯片进入打嗝模式,便于芯片减少转换功耗;当 电压高于5.2 V时,齐纳二极管发生击穿,电流流入 地端(GND)。

固体电子学研究与进展

故障品:(a)失效相关电路;(b)仿真结果;(c)实测结果 Fig.6 Failed sample: (a) Fault-related circuit; (b) Simulated result; (c) Test result

## 3.2 失效模拟与仿真分析

## 3.2.1 物理缺陷1仿真分析

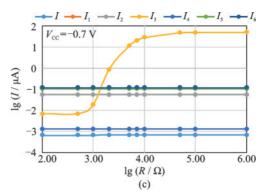

在失效分析中发现,物理缺陷1因为N-well掺 杂区域片电阻率大于P-body,所以增加了Region A1的电阻值。根据失效分析中所检测的物理故障 点电路位置及故障形态,将由R1A、R2A和R4A组成的 电阻模型加入到相关电路中,如图7(a)所示。为了 与失效分析结果比对,将芯片电源端偏置电压  $(V_{cc})$ 分别设置为  $1.8 \ V_{s} - 0.7 \ V_{s}$  然后改变电阻  $R_{1A}$ 、 $R_{2A}$  和  $R_{4A}$  的阻值来监控主要电路的电流变化  $(I_1-I_6)$ 。电流(I)随着电阻(R)变化而变化的曲线如 图 7(b)、(c)所示,当偏置电压为 1.8 V 时,电路电流

图 7 物理缺陷 1: (a) 相关电路; (b) 正向偏压仿真结果; (c) 反向偏压仿真结果

Fig.7 The physical defect 1: (a) Related circuit; (b) Emulation result by forward bias; (c) Emulation result by reverse bias

没有明显变化;当偏置电压为反向(-0.7 V)时,电路电流变化结果与失效分析测试结果吻合,如图 7 (c)所示,证实了物理缺陷 1 对电流的改变主要体现在  $I_2$ 和  $I_4$ 。因为改变了集成电路内部相关电路中的比较器 U7A、U6A 一端的电阻值,进而改变了电位值,最终引起的芯片输出的变化。

根据实际测试的正常品与故障品的电流变化量( $\Delta I$ ),可以模拟出模型中电阻  $R_{1A}=R_{2A}=R_{4A}=110~\Omega$ (当 $V_{CC}=-0.7~V$ , $\Delta I=560~\mu A$ 时)。

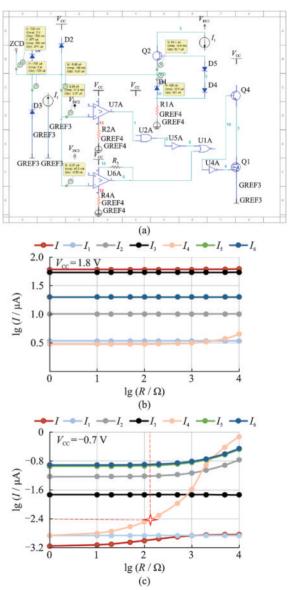

## 3.2.2 物理缺陷 2 仿真分析

在失效分析中发现,物理缺陷 2 更大范围的结掺杂范围导致了基级(Base)和集电极(Collector)之间的导通电阻增大。根据这种物理缺陷在电路中所在位置和缺陷的具体形态,将  $R_{5A}$  电阻模型加入到相关电路中,如图 8(a) 所示。为了与失效分析结果比对,将电源端偏置电压分别设置为 1.8 V、-0.7 V,然后改变  $R_{5A}$  的阻值来监控主要电路的电流变化  $(I_1 - I_6)$ 。电流随着电阻变化而变化的曲线如图 8(b)、(c) 所示,当偏置电压为-0.7 V 时,电路电流变化很小,可以忽略;当偏置电压为 1.8 V 时,电路电流变化很小,可以忽略;当偏置电压为 1.8 V 时,电路电流变化很小,可以忽略;当偏置电压为 1.8 V 时,电路电流变化银小,可以忽略;当偏置电压为 1.8 V 时,电路电流变化银小,可以忽略;当偏置电压为 1.8 V 时,电路电流变化银小,可以忽略;当偏置电压为 1.8 V 时,电路电流变化银外,可以忽略;当偏置电压为 1.8 V 可以忽略;

根据实际测试的标准品与失效样品的电流变化量( $\Delta I$ ),可以模拟出型中电阻 $R_{5A}$ =7 k $\Omega$ (当 $V_{cc}$ = 1.8 V,  $\Delta I$ =60  $\mu$ A 时)。

(b)

图 8 物理缺陷 2: (a) 相关电路; (b) 正向偏压仿真结果; (c) 反向偏压仿真结果

Fig.8 The physical defect 2: (a) Related circuit; (b) Emulation result by forward bias; (c) Emulation result by reverse bias

#### 3.2.3 输出波形仿真分析

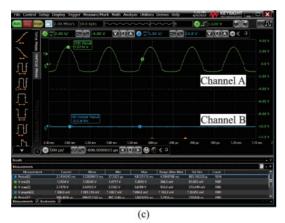

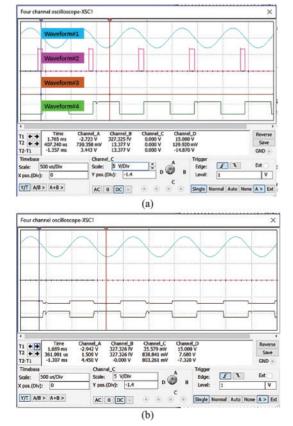

从上述仿真分析结果得出,物理缺陷1和2均对集成电路的电气性能产生影响。根据这两种缺陷,将缺陷模型评估的电阻 $R_{1A}$ 、 $R_{2A}$ 、 $R_{4A}$ 和 $R_{5A}$ 均加入电路,如图9(a)所示,电路仿真输出波形如图9(b)所示,同时对故障进行实际输出波形的检测分析,输出波形如图9(c)所示。实际输出结果与仿真结果一致,即无法产生输出。

利用 Multisim 内置的探针检测功能,对内部重要电路相关的波形进行输出检测,正常品的波形输出如图 10(a) 所示。在模拟电路中加入物理缺陷 1

固体电子学研究与进展

图 9 物理缺陷 1 和 2: (a) 相关电路; (b) 电路仿真输出波形; (c) 实际检测输出波形

Fig.9 The physical defects 1 and 2: (a) Related circuit; (b) Emulation result of output waveform; (c) The detected output waveform

图 10 重要电路监测波形:(a)正常品;(b)加入物理缺陷1和2 Fig.10 Important waveform monitoring: (a) Good reference sample; (b) With the physical defects 1 and 2

和2的等效模型,发现实际影响波形输出的关键部 件为电阻 R<sub>4A</sub>, 检测波形如图 10(b) 所示。因为这个 物理损伤点,内部电路的比较器 U6A 无法正常输出 低电平。在这个案例中,因为缺陷电阻 $R_{4A}$ 的引入, 实际输出低电平时的电压数值接近7.8 V。这致使 U1A 无法拉低到低电平, 三极管 Q1 无法打开, 最终

导致芯片无法输出低电平。

引入物理缺陷1和2的等效模型后的电路的仿 真结果显示,物理缺陷点1引发了芯片的失效。

#### 结 论

本文针对集成电路复杂的电性能故障和参数 失效模式,提出了一种新的基于缺陷模式的 Multisim电路模拟和仿真分析方法。基于集成电路故障 模式的分析,利用失效分析技术检测集成电路内部 的故障损伤点,依据物理缺陷位置和形式建立模型 进行物理缺陷模型的和仿真分析,进而确定物理损 伤点对于复杂电路的真实贡献和失效过程,以此来 解决目前集成电路的功能失效难以判定、失效的过 程与根本原因难以追溯的困境。尤其对于复杂且 存在多个物理缺陷的案例,通过仿真分析的手段可 以评估不同缺陷形式对芯片的相关电路的电压电 流的贡献,也能评估对最终电气性能的影响。这对 于找到真正失效的源头、失效分析和可靠性检测技 术的提升有着重要意义。

## 参考文献

- [1] 武咏琴,卜伟海,康劲,等.3 nm以下技术代FinFET 及围栅器件的发展与挑战[J]. 微纳电子与智能制造, 2021, 3(1): 14-26.

- [2] 邓惠雄,魏苏淮,李树深.宽禁带半导体掺杂机制研 究进展[J]. 科学通报, 2023, 14(68): 1753-1761.

- [3] 田飞飞,凌显宝,张君直,等.晶圆级异构集成3D芯 片互连技术研究[J]. 固体电子学研究与进展, 2023, 43(3): 287-288.

- [4] 陈选龙,李洁森,黎恩良,等.基于失效物理的集成电 路故障定位方法[J]. 半导体技术, 2019, 44(4): 1753-1761.

- [5] 龚瑜. 电源管理 IC 失效模式验证及定位方法[J]. 半导 体技术, 2018, 43(5): 394-400.

- [6] 龙冼, 杜雯, 孙增林. 基于模拟元件的保护电路设计 [J]. 无线互联科技, 2019, 16(7): 68-70.

- [7] 胡家兴,景博,黄以锋,等.QFP封装互连结构电气特 性建模与退化分析[J]. 电子学报, 2019, 47(2): 366-373.

**龚** 瑜(GONG Yu) 女,1988年生,湖 南张家界人,在职研究生,主要研究方向 为集成电路失效分析与可靠性提升。