# 基于 FPGA 的 μ子鉴别器读出系统前端电路

陈一新 梁 昊 薛俊东 刘 强 刘宝莹 周 雷 虞孝麒 周永钊 (中国科学技术大学近代物理系 合肥 230026)

摘要 介绍了北京谱仪第三代工程(BESIII)中的 μ子鉴别器读出系统的前端电路设计,包括系统的结构、各部件的基本功能和工作原理、触发选通逻辑的设计和系统防干扰等关键问题的设计思路和实现方法,以及采用FPGA的实现过程。经过系统检测,前端电路及其组成的数据链全部实现了预期的设计目标。

关键词 FPGA, μ子鉴别器,前端电路中图分类号 TL822

对传统的高能物理数据获取系统前端电路而 言, 其前置放大器往往置于探测器内部或附近, 由 电缆将模拟信号送到远端的主放大器和数字电路进 行信号处理。此法的缺点是模拟信号传输易受干扰。 鉴此, 高能物理实验数据获取系统希望在前端电路 中就实现数字化、将数字化数据通过长电缆线传送 到远端的数字信号处理系统中。事实上,探测器内 部空间的有限,在其内部实现复杂的电路功能,成 为前端电路(FEC. Front End Card)设计的主要难点 之一。µ子鉴别器读出系统是北京谱仪第三代(BES III, Beijing Spectrometer III)工程的重要组成部分,前 端电路是读出系统的核心部件。根据工程具体要求, 我们研制了基于 FPGA(Field Programmable Gate Array)的 µ子鉴别器读出系统前端电路,采用 Verilog 语言编写逻辑, 在 Altera EP1K30TC144-3 型 FPGA<sup>[1]</sup>上实现了前端数字脉冲信号的流水线缓 冲存储、触发选通和解随机缓存的全部功能。

# 原理

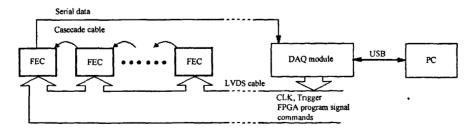

BESIIIμ子鉴别器读出系统原型机主要由前端 的数据链和后端的数据读出插件组成。读出系统共 有 40 条数据链, 每条数据链包括 16 块 FEC。每块 FEC 负责采集阻性板室(RPC)探测器 16 路通道的人 射粒子位置信号[2],通过甄别器转换成数字脉冲信 号送入 FPGA, 在 FPGA 内部使用流水线技术延时, 等待触发信号(Trigger)的选通,将收集到的好事例 数据存入事例缓冲器,最后由并串转换器产生单板 串行数据。16 块 FEC 间采用菊花链方式级联,并 由处于数据链末端的 FEC 将一条链的 256 个通道的 串行数据通过 30 m LVDS 差分信号传输至后端数 据获取插件。最后由数据获取插件通过 USB 接口将 数据传送至 PC 机。数据读出插件负责对数据链 16 块 FEC 进行 FPGA 编程、发送控制命令等功能。系 统工作时钟为 20 MHz。读出系统原型机结构如图 1 所示。

## 1 μ子鉴别器读出系统原型机组成及工作

图 1 μ子鉴别器读出系统原型机组成 Fig.1 Prototype of muon counter

国家大科学工程北京正负电子对撞机升级项目(BEPCII)资助

第一作者: 陈一新, 男, 1977 年出生, 2005 年于中国科学技术大学近代物理系物理电子学专业获博士学位

通讯作者: 梁 昊

收稿日期: 2007-09-10, 修回日期: 2007-11-06

# 2 前端电路结构设计

## 2.1 FEC 模拟部分概述

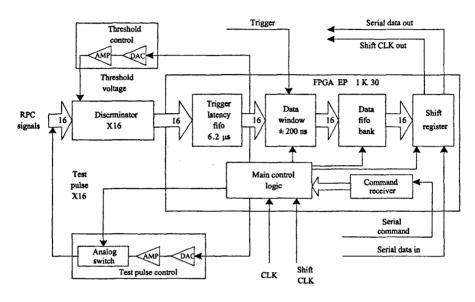

FEC 结构如图 2 所示。甄别器由 4 片比较器 ADI CMP401 组成;负责对 RPC 探测器产生的 16 个通道的模拟脉冲信号进行甄别,幅度高于阈值的模拟脉冲经甄别产生相应的数字脉冲信号。阈值控制电路由 DAC 芯片 TLC7528 和一级运放(LM324)

射随电路组成;FPGA 接受数据获取插件传送的命令,控制相应的 DAC 码,产生相应的阈值电平。测试脉冲产生电路由 DAC 和模拟开关 CD4066 组成;FPGA 接受数据获取插件传送的测试命令,产生相应的极窄的数字控制脉冲,模拟开关在此脉冲控制下瞬间打开又立刻关闭,产生模仿 RPC 信号的模拟脉冲,用以测试甄别器和 FPGA 的性能。

图 2 FEC 的结构 Fig.2 Schematic diagram of the FEC

## 2.2 触发选通逻辑设计

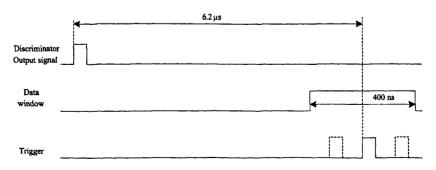

RPC 探测器的位置信号经过甄别后变成了相应的位置数据;该数据是否是一个好事例,必须等待 Trigger 信号的选通。Trigger 信号的产生比相应的 RPC 脉冲延迟 6.2 μs,且 Trigger 信号存在 ±200 ns 的晃动。因此甄别器产生的位置数据进入 FPGA后,首先要经过 6.2 μs 的流水线延迟,然后展宽成

一个宽度为400 ns(200 ns×2)的数据窗口。在Trigger 不晃动的情况下,Trigger 单宽度脉冲应位于数据窗口的中央;而当 Trigger 发生晃动时,其晃动范围始终落在数据窗口之内。这就保证了系统不会因Trigger 信号的晃动而丢失好事例。触发选通时序如图 3 所示。

图 3 触发选通时序 Fig.3 Timing waveform of data strobe

图 2 中的主控逻辑模块是整个逻辑中最重要的部分,它根据其他部件的工作状态,产生相应的内部控制信号;例如根据数据缓冲的空满状态产生读写使能信号,根据数据移位状态产生并串转换器的移位控制信号、移位时钟等。

并串转换器是移位寄存器,并行写人的好事例数据,根据串行移位时钟的节拍进行移位,形成串行数据。由于移位过程中移位寄存器不能进行并行写人,为了避免丢失此期间到来的下一个好事例的数据,经过 Trigger 信号符合后的 16 个通道的脉冲信息,须作为好事例数据存人数据缓冲存储器(图 2中的 FIFO Bank);当前的串行数据移位过程完成后,主控逻辑模块才能让新的事例数据从数据缓冲存储器中读出,并行写人移位寄存器启动新一次的移位过程。因此,主控逻辑模块启动串行数据移位过程。同时满足:1) 当前的数据缓冲存储器非空,即有数可读; 2) 移位寄存器处于空闲状态,即当前并未进行移位过程。

## 2.3 命令接收模块

图 2 中的命令接收模块是串并转换移位寄存器,主要负责接收数据获取插件发送过来的串行命令并对其进行解码。命令格式设计为 24 位;高 8 位为命令头,用来识别命令的种类;低 16 位为数据位,用来承载该命令携带的数据信息。命令主要有:1) 阈值设置和测试脉冲幅度设置,其电平对应的DAC的码值放在命令的 16 位数据位中; 2) 16 个通道的模拟开关控制,数据位中存放着该时刻 16 个模拟开关的通断信息,系统测试时 RPC 模拟信号的产生即通过该命令; 2) 数据获取插件收到正确事例数据后返回的确认信息,负责 FEC 和数据获取插件之间的握手。

### 2.4 FEC 的防干扰措施

μ子鉴别器读出系统前端电路处于探测器内部,工作环境恶劣,且与后端数据获取插件的电缆

连接有 30 m。FEC 和传输电缆都有可能受地线干扰及空间电磁干扰,甚至导致系统无法正常工作。研制过程中遇到的主要干扰问题是: 1) FPGA 的编程控制信号受到干扰导致 FPGA 的逻辑消失; 2) 触发信号受到干扰产生"假 Trigger",造成误触发; 3) 串行数据在传输过程中受到干扰,导致数据获取插件收到的数据出错。

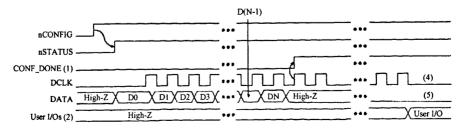

Altera 的 FPGA 的编程方式最常用的是 PS 方式 (Passive Serial)<sup>[3]</sup>,和编程相关的信号线有 5 条: nConfig、nStatus、Data0、DCLK 和 Conf\_Done,平时 nConfig 为高电平。编程过程中,数据获取插件使 nConfig 发出低脉冲,FPGA 检测到 nConfig 上升沿后开始做初始化工作,清除内部逻辑,将 I/O 引脚置成三态,将 Conf\_Done 电平置低;稍后 nStatus 信号跳变表示可以进行编程,配置芯片发出编程数据 Data0 和编程时钟 DCLK;编程完成后 FPGA 释放 Conf\_Done 引脚,其电平被上拉置高表示编程成功。编程时序如图 4 所示。

实际工作过程中,nConfig 信号易受外部干扰产生错误的脉冲,致使 FPGA 误认为启动了新一次的编程而使内部逻辑消失。根据实验测量,外部干扰的峰脉冲宽度一般<10 ns。我们采取的措施是加宽 nConfig 信号的脉冲宽度,使其宽度>10 ms;并在 nConfig 信号线上加入上拉电阻和下拉电容。通过适当调节阻值和容值,可使宽度<10 ns 脉冲全部被过滤,保证了编程信号的稳定性。

Trigger 信号也会受外部干扰产生尖峰脉冲,导致误触发。我们采取的针对性措施是改变 Trigger 信号的脉冲宽度和接收逻辑,超过一定宽度的脉冲才被认为是真正的 Trigger 信号,这样窄宽度的干扰脉冲就被接收逻辑丢弃。此外,在 PCB 的触发信号走线上串接铁氧磁珠,也能减少尖峰脉冲的影响。

针对串行数据传输过程受干扰产生的错误,我们在数据的编码上采取了相应的措施。首先,对一条数据链的第一块和最后一块 FEC 的串行数据部分,分别加入7位的数据头和数据尾;数据获取插

图 4 PS 方式编程时序<sup>[2]</sup>

Fig.4 Timing waveform of PS mode configuration

件接收到串行数据后先对此进行判断,如数据头尾 损坏,则丢弃该数据。其次, 在每块 FEC 的 16 位 串行数据前加入一位奇偶校验位,一旦数据在传输 过程中发生错误,数据获取插件能对数据进行奇偶 校验, 判断每块 FEC 的数据是否完好, 进一步增强 了串行数据的容错能力。再者, 串行数据发送后, FEC 不立刻将当前数据从数据缓冲中清除。数据获 取插件在正确识别出一次好事例的串行数据后,会 发送一个确认信号 ACK 给 FEC, FEC 在规定时间 内收到 ACK 后,才可清除当前数据,启动下一次 的发送过程: 否则, FEC 认为此次数据发送出错, 并将当前数据重新写入并串转换移位寄存器, 重新 发送该数据。这样的"出错重发"机制在最大程度上 保证了好事例数据的正确性和完整性。最后,我们 在每块 FEC 的电源输入端加入共模轭流圈; PCB 设计采用六层板、提供独立的模拟地层、数字地层 和模拟信号层; 为每块 FEC 加装金属屏蔽盒; 为 30 m 传输电缆和电源线加上金属保护外套。这些措 施都显著降低了外部干扰对系统的影响, 保证了系 统工作的稳定性。

## 3 系统测试

测试时由 PC 机发出命令,对数据链上的 16 块 FPGA 进行远程编程,设置好合适的阈值和测试脉冲幅度。然后由数据获取插件产生伪随机开关信号和相应的 Trigger 信号送给 FEC,模仿真实 RPC 探

测器被粒子击中时的情形。测试内容包括:(1)阈值及测试脉冲幅度电平是否符合预期值。(2)系统在长时间工作条件下性能是否稳定,是否有数据丢失等情况发生。(3)系统在外部强干扰作用下是否能保持传输数据的正确和完整。

经测试, FEC 的阈值及测试脉冲幅度设置功能完好; 系统在平均触发率 4 K 条件下 12 h 内取数正确, 未发生数据错误、丢失的情况; 在外部电器连续频繁开关 200 次以上产生的强干扰环境下, 系统取数正常, 未发生错误。

#### 4 结语

本文描述了基于 FPGA 的 μ子鉴别器读出系统 前端电路设计,详细论述了其 FPGA 逻辑的设计与 实现,以及系统采取的各种防干扰措施。本设计对 研究和利用 FPGA 实现高能物理实验的前端数据采 集技术提供了有益的参考。

#### 参考文献

- 1 ACEX 1K Programmable Logic Device Family Data Sheet, Altera Corporation

- 2 Cavallo N, Fabozzi F, Parascandolo P, et al. Front-end card design for the RPC detector at Babar. INFN/TC-96/22

- 3 Configuring SRAM-Based LUT Devices. Altera Corporation

#### Front-end card of muon counter using FPGA chips

CHEN Yixin LIANG Hao XUE Jundong LIU Qiang LIU Baoying ZHOU Lei YU Xiaoqi ZHOU Yongzhao

(Department of Modern Physics, University of Science and Technology of China Hefei, Anhui 230027, China)

Abstract Development of front-end card of muon counter for the BES III (Beijing Spectrometer III) project is presented in this paper. The system structure, functions of the components, strobe logic design, anti-jamming and realization with FPGA are introduced. The front-end card and data-chain worked perfectly under the given conditions, and the design goals were achieved.

Key words FPGA, Muon counter, Front end card CLC TL822