文章编号: 1007-4627(2023)02-0229-08

# 基于FPGA的星上eMMC存储系统

隗彦伟,王东<sup>†</sup>,陈燃,王辉,杨远康,周世强, 周卓,刘慧迪,李牧宪,温佳奇

(华中师范大学物理科学与技术学院像素实验室, 武汉 430079)

摘要: X射线偏振探测立方星载荷 (China Space X-Ray Polarization Detection System, CXPD) 致力于检测空间 X射线偏振度、能谱等信息,用于理解天体物理现象。为满足安全性强、功耗低、成本低的小型卫星载荷存储需求,本工作选择具有错误检查和纠正、掉电保存、坏块管理等功能的内嵌式多媒体存储卡作为存储介质。针对卫星载荷在太空特殊环境下的上电操作和星载设备的数据吞吐量需求,结合 eMMC5.0 协议,研究了基于现场可编程门阵列 (FPGA) 控制的星上存储系统。该系统在高低温试验测试、振动测试和长时间 alpha 源照射测试中均能稳定运行。

**关键词:** X 射线; eMMC; FPGA; 安全性

中图分类号: TP311 文献标志码: A DOI: 10.11804/NuclPhysRev.40.2022058

## 0 引言

随着天体物理领域的不断探索,空间探测技术不断 提升,对立方星存储技术的要求越来越高,国际上最早 研究存储的美国SEAKR公司,在航天大容量存储研究 方面处于领先位置,该公司产品中的 ModMesh 系列, 以Flash为存储介质,最大容量高达16 Tbits,数据传输 带宽高达 36 Gbps<sup>[1]</sup>; 美国 CALCULEX 公司研发的可 拆卸 FlashCache III 模块,以 Flash 为存储介质,在极严 苛环境下,数据写入读出速率可以达到44 MB/s,现已 应用在美国空军 F-15 战机中 [2]。中国科学院空间应用 中心研制了我国第一批星载固态存储器,以SDRAM为 存储介质,存储带宽为1 Mbps,容量为512 Mbits<sup>[3]</sup>; 我国发射的嫦娥二号探月卫星,以NAND Flash为存储 介质,存储容量高达128 Gbits,数据输入速率超过256 Mbps<sup>[4]</sup>。NAND Flash 非易失性存储单元是近几年一直 采用的存储技术,但是由于存在位偏转、坏块和稳定性 差等问题<sup>[5]</sup>, MMC协会将高精度 NAND Flash 和 Flash 控制器集成在一块小型的BGA芯片中,这种新型的内 嵌式多媒体存储卡 (Embedded Multi Media Card, eM-MC)芯片具有高容量、高稳定性、坏块管理、ECC校 验等技术,现已在手机和平板电脑方面广泛使用[6]。

本项目为X射线偏振探测立方星载荷提供存储方案,

该立方星载荷基于 Topmetal-II 像素芯片,用于在空间中检测 X 射线 (2~10 keV) 偏振度、能谱等参数 <sup>[7-8]</sup>。硬件方面 FPGA 芯片选用 Xilinx 的 Kintex-7,数据存储选用镁光 MTFC64GAJ eMMC 芯片。软件方面基于 eM-MC5.0协议,实现数据读写,满足项目数据吞吐量的需求。

## 1 eMMC控制系统整体技术方案

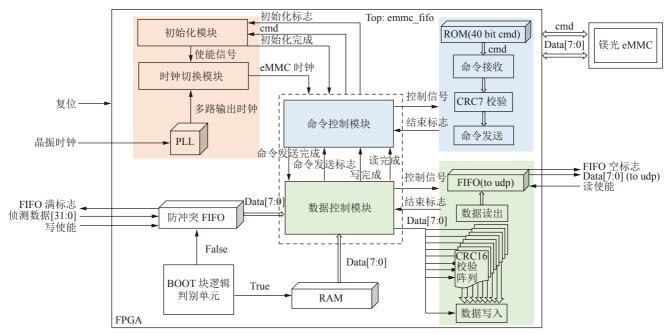

本方案基于 Kintex-7 系列的 FPGA 芯片 XC7K70TF-BG676,实现了对镁光 eMMC 芯片的总体控制。方案中设计了数据控制模块、命令控制模块、初始化模块、时钟切换模块,并最终封装成一个 FIFO IP 核,便于使用,结构框图如图 1 所示。

## 1.1 eMMC5.0协议

eMMC协议的IO接口如表1所列。在CLK接口方面,为降低系统功耗,本文选择High Speed SDR模式 (0~52 MHz),结合设计的BOOT块,整体读写速度满足项目要求。CMD接口共支持63条命令,功能各不相同,如擦除、发送当前状态、进行读操作等,本文根据项目具体情况,选择相关命令。DATA接口共8bit通道,通过CMD6选择1/4/8bits位宽,DATA[0]用作忙信号标志位和CRC校验返回值。

收稿日期: 2022-05-06; 修改日期: 2022-07-27

基金项目: 国家自然科学基金资助项目(11875146, U1932143)

作者简介: 隗彦伟(1997-), 男, 黑龙江哈尔滨人, 硕士研究生, 从事信息与通信工程研究; E-mail: 941648611@qq.com

†通信作者: 王东, E-mail: dongwang@mail.ccnu.edu.cn

图 1 eMMC控制器总体结构框图(在线彩图)

表1 协议IO接口

| 接口             | 功能                                 |  |  |  |  |

|----------------|------------------------------------|--|--|--|--|

| CLK            | 单向端口,FPGA提供eMMC工作时钟。               |  |  |  |  |

| CMD            | 串行双向端口,FPGA提供命令,eMMC提供响应。          |  |  |  |  |

| DATA[7:0]      | 并行双向端口,FPGA提供写入数据,eMMC提供响应和读出数据。   |  |  |  |  |

| RESET          | 单向端口,FPGA提供eMMC硬复位。                |  |  |  |  |

| Data<br>Strobe | 单向端口,eMMC提供返回时钟信号,仅在HS400模式<br>使用。 |  |  |  |  |

## 2 各模块介绍

### 2.1 系统初始化模块

eMMC在上电之后,进行硬件复位进入IDLE状态,初始化阶段时钟不得超过400 kHz。协议规定等待大约1 ms后,发送CMD1进行OCR寄存器的验证。对于容

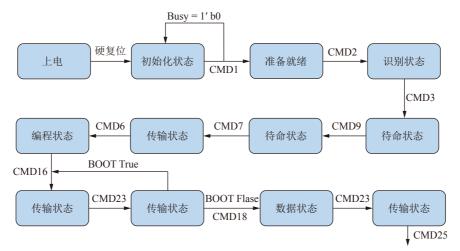

量大于 2 GB的 eMMC返回的值有两种: 0x40FF\_8080和 0xC0FF\_8080,两者的差异在于最高位(busy bit),若最高位为 0,则循环发送 CMD1,直到最高位出现 1,随之进行其他命令的发送。CMD6 的发送进行两次,配置工作时钟频率模式和传输数据有效位宽,根据项目需求,这里选择 High Speed SDR模式 (0~52 MHz)和 8 比特位宽,至此 eMMC 协议中规定的初始化流程结束 [9],时钟切换为 50 MHz。由于星上不定时关机和读写速率的原因,引入 BOOT块,将 BOOT块的读写加入初始化中,初始化顺序如图 2 所示。

### 2.2 数据控制模块

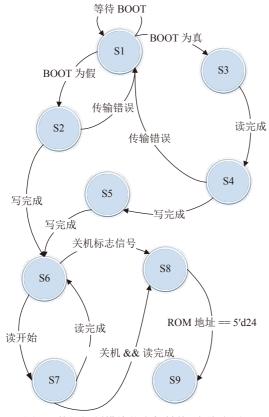

数据控制模块包括了读写两部分,使用状态机将流程分为9个状态进行跳转,如图3所示。

图 2 eMMC 初始化命令转换(在线彩图)

图 3 数据控制模块状态机转换(在线彩图)

S1-初始状态,进行BOOT块的读取;S2-BOOT块数据写入eMMC中;S3-读取断电前不足16384Byte的数据,同时写入到位宽为8,深度为16384的RAM中;S4-BOOT块数据写入eMMC中;S5-RAM中数据填补,同时RAM数据写入eMMC;S6-防冲突FIFO数据写入eMMC中;S7-读取eMMC存储数据;S8-卫星关机前,两次eMMC写入数据操作;S9-卫星关机,状态跳转结束。

在 eMMC 写模块中,写操作通过 CMD23(给定 Multiple block模式中 block数)和 CMD25(给定当前写入 eMMC 的地址)配合使用,CMD23 中 block 数始终设为 32。由于 CMD16 中参数设为 512,所以 CMD25 中地址 每加1,代表写入了 512 Byte 的数据。

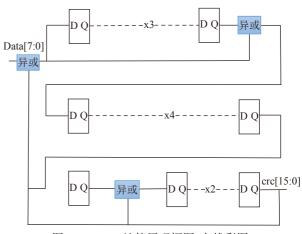

eMMC 5.0 协议规定,在数据最后一位传输结束后,需发送数据校验值,产生校验值的算法为 CRC16/

CCITT,所以对于准确性和实时性的要求较高。CRC 校验码为 16 bits,生成多项式为 17位。数据流左移 16位,再除以生成多项式,做不借位的除法运算(相当于按位异或),所得的余数就是 CRC 校验码 [10]。特别注意 CRC16/CCITT 输入以字节为单位进行反转,输入设为 1 bit,需多加考虑每次反转问题,所以输入设为 8 bits。CRC16 计算框图如图 4 所示。

图 4 CRC16 计算原理框图 (在线彩图)

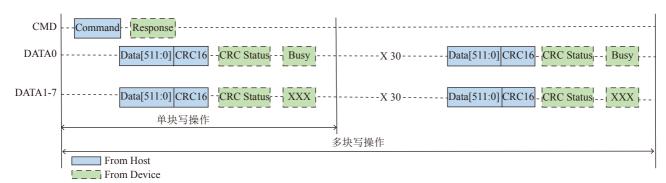

eMMC 写操作过程中,使用 DATA0 作为忙信号,如图 5 所示。每成功写入 512 Byte 的数据,eMMC 会进入 Program状态。DATA0 信号线拉低 (默认为高) 作为写数据忙信号,eMMC 会阻塞主机的 IO request<sup>[11]</sup>,且忙信号在每次上电后的第一次写入时间较长,经测试,时间为 1 ms,引入 BOOT 块,将第一次的写操作提前完成,再写入有效数据时,忙信号时间缩减 55%。

eMMC读模块中,读操作通过CMD23(给定Multiple block模式中block数)和CMD18(给定当前读入eM-MC的地址)配合使用。eMMC读操作过程中,读命令发送完毕,DATA端口主动拉高,如图6所示。在每次上电后的第一次 $N_{AC}$ 时间较长,引入BOOT块,将第一次的读操作提前完成,在读出有效数据时,DATA端口主动拉高时间大大缩减。

图 5 数据写入 eMMC 过程(在线彩图)

图 6 eMMC 读出数据过程(在线彩图)

#### 2.3 BOOT块设计

卫星载荷运行期间,侦测到的 X 射线相关信息,全部缓存到防冲突 FIFO 中,再存储到 eMMC 中。在突发 X 射线暴情况下,会出现有效数据量骤增问题。由于 eMMC 初始化所需时间较长,因此防冲突 FIFO 的设计深度需要尽可能大。因此,本文将 FPGA 片上 60%的 BRAM 资源用来作为 FIFO 缓存。

eMMC 写操作选择 Multiple-block write 模式,块数为32,由此设计的防冲突 FIFO 中 prog\_full 信号的触发条件参数设为32×512=16 384,在 prog\_full 信号拉高时,eMMC 可进行一次写入操作。立方星运行中,南北极和南大西洋异常区信号的干扰较大,需关机运行 [12]。若防冲突 FIFO 中数据量未达到 16 384,断电即会数据丢失,严重影响数据分析。因此,需要设计 BOOT 块解决关机前的数据存储问题。

卫星载荷关机时会提前发出关机指令,此时防冲

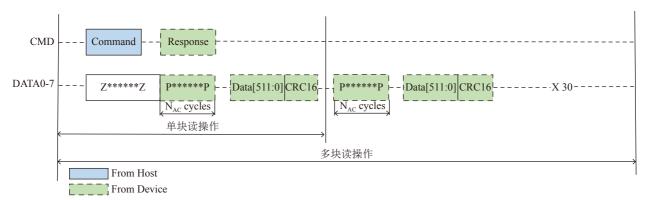

突 FIFO 停止数据写入,判断 prog full 信号,高电平即 进行正常 32 块 乘以 512 bits 的有效数据写入 eMMC; 低电平需判断防冲突 FIFO 输出的 empty 信号, 若为高 电平,说明此时防冲突FIFO内无数据,跳转到结束状 态,eMMC停止工作。若 empty 信号为低电平,将防冲 突 FIFO中有效数据存入深度为 16 384、位宽为 8 的 RAM中, RAM中未填满区用0填充,并同时执行写命 令,写入eMMC中,使用一级流水线,加快关机前eM-MC操作的运行速度。至此, 侦测的所有 X-ray 数据全 部存储到 eMMC,之后进行 BOOT块的编写。该 BOOT 块由 16 位的帧头"0x5050"、32 位的 eMMC 中残 缺块(不足16384 bits的有效数据和0补充的数据)起始 地址位、32位的RAM中有效数据地址位、32位的eM-MC读操作后地址信息和400位无效数据"0"构成,如 图 7 所示。通过移位寄存器循环 32 次,写入 eMMC 的 起始地址中, 为卫星载荷重新上电后的读操作做准备。

图 7 BOOT 块结构构成(在线彩图)

卫星上电及eMMC初始化完成后,先进行BOOT 块的读出并判断帧头是否匹配,若匹配错误,用0刷新BOOT块,完成第一次eMMC的写操作。全零BOOT 块成功写入eMMC之后,eMMC的写入地址重新回到0x20。若匹配正确,则继续读取eMMC残缺块的数据,同时存入深度为16384、位宽为8的RAM中,用0刷新BOOT块,完成第一次全零BOOT块的eMMC写操作。RAM中未填满区等待prog\_full拉高,用防冲突FIFO中有效数据填充,并且eMMC的写入地址变为上次断电前eMMC中残缺块起始地址位,至此BOOT块运行流程结束。

引入BOOT块的另一个优势可以把eMMC的读写

性能提高,因为在eMMC上电后第一次写入和读出时, 有一段较长的忙信号时间,先进行一次BOOT块的读写, 可以在正常写入读出时提前渡过第一个忙信号时间。

## 2.4 命令控制模块

命令控制模块包括发送和接收两部分。命令发送模块中使用ROM存调试好的24条CMD命令,功能各不相同,命令长度为48 bits,包含起始位0,主机从机选择位1,6比特索引位,32比特参数,CRC7校验和结束位1。待命令发送完毕,2~64个时钟周期后eMMC在CMD接口会返回响应,共五种类型,R1、R3、R4、R5长度为48 bits,包含起始位0,主机从机选择位0,6比特索引位,32比特设备状态参数,CRC7校验和结

東位1。R2长度为136 bits,包含起始位0,主机从机选择位0,6比特索引位,127比特 CID或 CSD参数和结束位1<sup>[13]</sup>。命令接收模块通过136 bits长度的移位寄存器寄存响应的数值,根据移位寄存器的响应参数判断CMD命令发送是否成功。

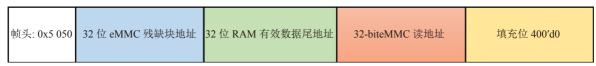

#### 2.5 时钟控制模块

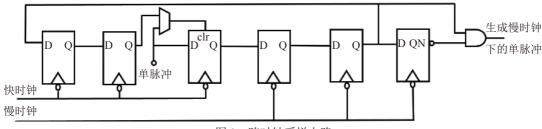

本项目所用时钟共4个,由PLL锁相环输出的相位相同的50/100/125 MHz时钟和一个由50 MHz分频的400 kHz时钟。通过使能信号,切换所需时钟,为避免切换时产生毛刺,采用了一种新型的电路结构<sup>[14]</sup>,如图8所示。

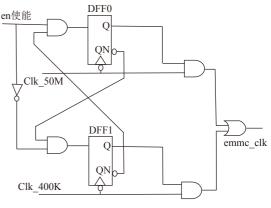

由于存在单比特的脉冲跨时钟处理的问题,50 MHz 时钟频率下采样125 和100 MHz 的脉冲,两个快时钟下

的脉冲对整个系统的运行起着很大作用,为保证成功采样,采用了一种新型的电路结构<sup>[15]</sup>,如图 9所示。

图 8 无毛刺时钟切换电路

图 9 跨时钟采样电路

## 3 测试结果及分析

#### 3.1 功能测试

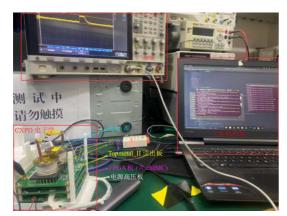

本项目组搭建了一套功能测试平台,如图 10 所示。通过 eMMC 存储有效数据,检测是否成功写入以及读出的数据是否正确。

图 10 eMMC 读写测试平台(在线彩图)

写入数据方面,发送一个512 Byte的数据后,等待eMMC在DATA[0]发送返回值,若为010,说明已成功写入;若为101,说明写入失败,需重新写入。写入失败的原因有很多种,CMD命令发送错误、数据高

低位顺序错误、CRC16结果错误等。本项目组自主研 发基于德国 XFAB350nm 工艺的 Topmetal-II 硅像素芯片, 长72 宽72, 共5 184 个像素点[16-17]。有效数据主要来 自于 AD9629 采样 Topmetal-II 芯片所侦测到的电压值, 采样分辨率 12 bits,为提高冗余容错率并方便数据分析, 在最高位补齐 4 bits 0,再加上 2 Byte 的地址信息,使 每个像素一次采样大小为4 Byte。在系统处于工作状态 时,其采样率为2 MHz,两块像素芯片同时工作。若芯 片所有像素均侦测到X射线,则有效数据产生速率的最 大值为 2×2 MHz×4 Byte=16 MB/s, 由此 eMMC 的写入 速度应大于16 MB/s。本文使用 Vivado 内 ILA IP 核进行 了信号抓取测试,在写入32×512 Byte 的数据的情况下, 大概需要47500个周期,平均速率为17MB/s,大于16 MB/s,满足速率需求。若未加BOOT块,第一次写入 的忙信号时间持续大概5万个周期,写入平均速率为 6 MB/s,不满足写入速度大于16 MB/s要求。

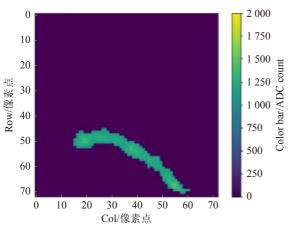

读出数据方面,发送读命令之后,有效数据从eM-MC通过以太网发送至上位机,并通过上位机程序进行检错,判断数据是否有丢失、错位等。经长时间测试,eMMC读写功能运行稳定,将检测到的alpha源径迹数据成功在上位机显示,如图11。其中,行列分别代表Topmetal-II芯片的72个像素点,右侧为color bar。

图 11 alpha 源径迹 (在线彩图)

#### 3.2 辐照测试

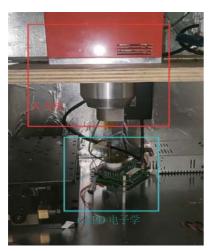

本项目选用 X 光机进行辐照测试如图 12 所示。本文将 X 光机直接对准 CXPD 电子学进行辐照测试,上方红色区域内为 X 光机,下方蓝色方框内是 CXPD 电子学系统。

图 12 X光机测试实物(在线彩图)

本文通过调整不同剂量的 X 光进行了长时间测试。 系统的数据来源于 AD9629 采样的原始数据,原始数据 量约为13.41 GB/h。数据样本越大,对辐照性能的测试 将有越强的参考性。

测试结果如下表 2 所列。本文将 X 光机剂量参数配置为 50 kV,1  $\mu$ A (kV代表 X 光机能量, $\mu$ A 代表电子数),共采集到 321.84 GB 大小的数据,未发现数据错误;

| 表 2 | 辐照实际测试数据表 |

|-----|-----------|

|     |           |

| 辐照类型 |                  | 总数据量/GB | 发生数据错误的大小/Byte |

|------|------------------|---------|----------------|

|      | X光: 50 kV, 1 μA  | 321.84  | 0              |

|      | X光: 50 kV, 10 μA | 379.16  | 0              |

|      | X光: 60 kV, 10 μA | 384.57  | 0              |

|      | X光: 60 kV, 20 μA | 382.21  | 2              |

将 X 光机剂量参数配置为 50 kV,10 μA,共采集到 379.16 GB 大小的数据,未发现数据错误。继续提高剂量,将 X 光机剂量参数配置为 60 kV,10 μA,共采集到 384.57 GB 大小的数据,未发现数据错误;最后将 X 光机剂量参数配置为 60 kV,20 μA,共采集到 382.21 GB 大小的数据,发现数据错误共 2 Byte。经过数据分析,发现在数据发生错误后,CXPD 电子学系统也能正常运行,后面的数据能正常读出。

#### 3.3 性能测试

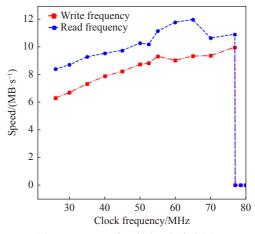

本项目选择 High Speed SDR(0~52 MHz)模式。在 eMMC5.0协议中,SDR模式读写操作的时钟范围为 26~52 MHz,为测试存储系统的极限速率以及检测系统的鲁棒性,将时钟提升到规定范围之外。在 alpha 源 30 min 连续取数下,时钟频率小于 76.9 MHz时,读写功能均能正常运行,误码率为 0,直到时钟超过 76.9 MHz,eMMC不能正常工作。26~76.9 MHz时钟频率下的数据的读写速度,如图 13 所示。为处理瞬时并发数据,双腔室最大事件率为 16 MB/s,eMMC工作频率为 30 MHz时,数据写入速率为 13 MB/s;工作频率为 40 MHz时,数据写入速率为 16 MB/s;工作频率为 50 MHz时,数据写入速率为 17.5 MB/s;为保证数据不丢失,最终将实际工作频率设为 50 MHz。

图 13 eMMC 读写性能(在线彩图)

## 3.4 高低温实验、振动测试

CXPD 电子学系统在中国空间技术研究院总装与环境工程部(北京卫星环境工程研究所),按照试验技术规范,如表3所列,在DL-5400-60电动振动试验系统和MPA712/M544A电动振动试验系统上完成了振动实验。

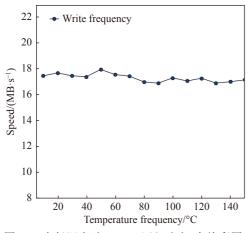

在高低温实验中,记录时钟频率为50 MHz时,通过以太网传输各温度下,eMMC写入速率的情况,如图14所示。通过测试,发现温度在10至150℃之间,存储系统性能参数达标,符合实验要求,无潜在隐患。

| <b>≠</b> 2 | <b>かが什・小田 生</b> |

|------------|-----------------|

| 表 3        | 实验技术规范          |

| 正弦震动    |                                            |           | 随机振动                                       |                        |

|---------|--------------------------------------------|-----------|--------------------------------------------|------------------------|

| 频率/Hz   | 量级/幅值(O-p)                                 | 频率/Hz     | 功率谱密度/( g <sup>2</sup> ·Hz <sup>-1</sup> ) | <del>一</del> 实验允许偏差    |

| 5~8     | 5.82 mm                                    | 20        | 0.006 0                                    | a.随机振动试验容差要求:          |

| 8~10    | 1.6 g                                      | 60~80     | 0.380 0                                    | 10~1 000 Hz ±1.5 dB    |

| 加载方向: 2 | 加载方向: <i>X、Y、Z</i> 三个轴向<br>扫描速率: 2 oct/min |           | 0.006 0                                    | 1 000~2 000 Hz ±3.0 dB |

| 扫描速率    |                                            |           | 0.006 0                                    | 随机振动总均方根加速度幅值: ±1.5 dB |

|         |                                            |           | 0.200 0                                    | b.试验持续时间: ±10%         |

|         |                                            | 600~700   | 0.200 0                                    | c. 正弦振动加速度幅值: ±10%     |

|         |                                            | 700~800   | 0.004 0                                    |                        |

|         |                                            | 800~1 200 | 0.004 0                                    |                        |

|         |                                            | 2 000     | 0.000 2                                    |                        |

|         |                                            | × 14 →    | · 田 加 末 座 体   7.5                          |                        |

总均方根加速度值: 7.5 grms 实验时间: 2 min/方向

实验方向: X、Y、Z方向

图 14 高低温实验 eMMC 写入速率 (在线彩图)

#### 4 结论

本文设计了一套基于 eMMC5.0 协议的小型卫星存储系统,存储容量达到 64 Gbit。本文采用 BOOT 块和一级流水线,在 High Speed SDR(50 MHz)模式下,写入速率大于 130 Mb/s,读出速率大于 82 Mb/s。本文解决了第一次写入时忙信号对整体读写速率的限制,并实现了星上断电防止数据丢失的功能。为了防范在空间辐射环境下半导体器件发生单粒子翻转效应,提高系统安全性,未来将增加抗辐射设计,代码设计层面上增加三模冗余、汉明码编码等<sup>[18]</sup>,并且结合 eMMC 自带的抗辐射命令 CMD30,在硬件层面上增加抗辐射水平。

#### 参考文献:

[1] LI Pan. Researdh of Key Technologies of Onboard Mass Storage Based on eMMC[D]. Harbin: Harbin Institute of Technology, 2017. (in Chinese)

- (李攀. 基于eMMC的星载大容量存储关键技术研究[D]. 哈尔滨: 哈尔滨工业大学, 2017.)

- [2] ZHANG Xianyu, ZHOU Changyi, AN Junshe. Computer Engineering and Design, 2021, 42(10): 2790. (in Chinese) (张贤玉, 周昌义, 安军社. 计算机工程与设计, 2021, 42(10): 2790.)

- [3] DONG Zhenxing. Research on Application of Spaceborne Solid State Recorder File Management Scheme[D]. Beijing: University of Chinese Academy of Sciences (National Center for Space Science, Chinese Academy of Sciences), 2017. (in Chinese) (董振兴. 星载固态存储文件化管理方案应用研究[D]. 北京: 中国科学院大学(中国科学院国家空间科学中心), 2017.)

- [4] TAN Weifeng, WANG Gan, DOU Jiao, et al. Journal of Northwestern Polytechnical University, 2020, 38(S1): 107. (in Chinese) (谭维凤, 王淦, 窦骄, 等. 西北工业大学学报, 2020, 38(S1): 107.)

- [5] LIU Jinjin. Design and Implementation of Embedded File System Based on NAND Flash[D]. Xi'an: Xi'an University of Electronic Science and Technology, 2021. (in Chinese) (刘金金. 基于NAND Flash的嵌入式文件系统的设计与实现[D]. 西安: 西安电子科技大学, 2021.)

- [6] LIU Baowen. Development of High-Speed and Largecapicity Storage Card Based on eMMC[D]. Harbin: Harbin Institute of Technology, 2015. (in Chinese)

(刘宝文. 基于eMMC的高速大容量存储卡研制[D]. 哈尔滨: 哈尔滨工业大学, 2015.)

- [7] ZHANG Shuangnan. Chinese Journal of Space Science, 2020, 40(5): 655.

- [8] ZOU Shuguang. High Spatial Resolution Radiation Imaging Detectors Based on Topmetal Sensors and CdZnTe Crystals[D]. Wuhan: Central China Normal University, 2017. (in Chinese) (邹曙光. 基于Topmetal芯片和碲锌镉晶体的高空间分辨辐射成像探测器[D]. 武汉: 华中师范大学, 2017.)

- [9] LIU Wei. Design and Implementation of eMMC Host Controller Based on AMBA Bus Protocol[D]. Changsha: Hunan University, 2020. (in Chinese) (刘伟. 基于AMBA总线协议的eMMC主机控制器的设计与实现[D]. 长沙: 湖南大学, 2020.)

- [10] PENG Wei. Journal of Nanjing University of Information Science and Technology:Natural Science Edition, 2012, 4(3): 258. (in Chinese)

- (彭伟. 南京信息工程大学学报(自然科学版), 2012, 4(3): 258.)

- [11] LAI Jiabin. Design and Implementation of High Speed eMMC Array Data Storage System Based on FPGA[D]. Nanjing: Nanjing University of Science & Technology, 2019. (in Chinese) (赖佳彬. 基于FPGA的高速eMMC阵列数据存储系统的设计与实现[D]. 南京: 南京理工大学, 2019.)

- [12] LIU Pengcheng. Research on the Effects that Solar Activityhas on the Single Event Effect for Space Instrument [D]. Changsha: National University of Defense Technology, 2016. (in Chinese) (刘鹏程. 太阳活动对空间仪器单粒子效应特性影响的研究[D]. 长沙: 国防科学技术大学, 2016.)

- [13] HOU Tianxi, LI Jinming, MA Lin, et al. Application of Electronic Technique, 2017, 43(9): 76. (in Chinese) (侯天喜, 李锦明, 马林, 等. 电子技术应用, 2017, 43(9): 76.)

- [14] ZHAO Baoyi, ZHAO Zhenhai, LI Guangliang, et al. Electronic Design Engineering, 2013, 21(21): 117. (in Chinese) (张宝宜, 赵振海, 李广良, 等. 电子设计工程, 2013, 21(21): 117.)

- [15] SONG Wenqiang, HU Yi. Microcontrollers & Embedded Systems, 2018, 18(9): 24. (in Chinese) (宋文强, 胡毅. 单片机与嵌入式系统应用, 2018, 18(9): 24.)

- [16] ZOU Shuguang, FAN Yan, SUN Xiangming, et al. Chinese Physics C, 2017, 41(4): 046003.

- [17] ZHANG Wei. Topmetal-II-Digital Readout Testing Method Research[D]. Wuhan: Central China Normal University, 2017. (in Chinese)

(张伟. Topmetal-II-数字读出测试方法的研究[D]. 武汉: 华中师范大学, 2017.)

- [18] ZHOU Fei, LI Qiang, XIN Tailin, et al. Spacecraft Environment Engineering, 2012, 29(4): 392. (in Chinese) (周飞, 李强, 信太林, 等. 航天器环境工程, 2012, 29(4): 392.)

## The FPGA-based eMMC Memory System Design for Satellite Payload

KUI Yanwei, WANG Dong<sup>†</sup>, CHEN Ran, WANG Hui, YANG Yuankang, ZHOU Shiqiang, ZHOU Zhuo, LIU Huidi, LI Muxian, WEN Jiaqi

(Pixel Laboratory, School of Physical Science and Technology, Central China Normal University, Wuhan 430079, China)

**Abstract:** China Space X-Ray Polarization Detection System(CXPD) is dedicated to detecting space X-ray polarization, energy spectrum and other information for understanding astrophysical phenomena. In order to meet the storage requirements of small satellite payloads with strong security, low power consumption and low cost, this paper selects embedded multimedia memory cards with functions of error checking and correction, power-down saving and bad block management as storage media. For the power-up operation of satellite payloads in the special environment of space and the data throughput requirements of satellite payload devices, combined with the eMMC5.0 protocol, this paper studies an on-satellite storage system based on field-programmable gate array(FPGA) control. The system can operate stably in high and low temperature test tests, vibration tests and long time alpha source irradiation tests.

Key words: X-ray; eMMC; FPGA; security