# 用于温度传感芯片的开关电容积分器的设计

郭建宁,陈文芗\*,冯勇建(厦门大学机电工程系,福建厦门361005)

摘要:设计了一种应用于温度传感芯片的全差分开关电容积分器.在温度传感芯片中,  $\Delta\Sigma$  调制器接收温度传感模块输出电压信号,并将模拟的电压信号转换成对应的数字信号.全差分开关电容积分器是  $\Delta\Sigma$  调制器中最核心的元件,它把接收到的温度传感器模块输出的模拟信号转换为数字信号.在开关电容积分器的实际设计中,存在  $\Delta\Sigma$  调制器中最核心的元件,它把阻和电荷注入、时钟溃通、采样尖峰等非理想因素.本文对这些非理想因素做了详细的分析,设计了一种全差分的开关电容积分器,可以抵消开关电容中电荷注入和时钟溃通带来的电压误差.同时,本文设计了一种全差分共源共栅放大器,可以很好的满足积分器的要求.从而提高整个系统的性能.

关键 词: 温度传感: 全差分开关电容积分器: △∑ 调制器: 全差分共源共栅放大器

中图分类号: TM 53

文献标识码: A

文章编号: 0438 0479(2007) 06-0792-05

20 世纪 90 年代中期,随着半导体和集成电路工艺的发展,智能化集成温度传感器应运而生,它是微电子技术、计算机技术和自动检测技术的结晶.智能温度传感器的最主要的特点是在系统中增加了 A/D 转换器,它能将信号处理电路和温度传感模块同时集成在一个芯片上.

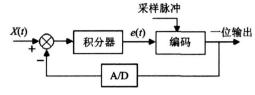

温度传感芯片主要由温度传感模块、& Σ调制器、 计数器、控制时钟模块、偏置和基准模块以及接口模块 六大模块组成[1] (如图 1 所示). 其工作原理如下: 温度 传感模块负责检测芯片上的温度信号,将温度信号转 换成与之相应的电压信号,并将电压信号进行前置放 大后送  $\Delta\Sigma$  调制器进行 A/D 转换.  $\Delta\Sigma$  调制器接收温 度传感模块输出电压信号后,采用过采样和噪声整形 技术将模拟的电压信号转换成对应的数字信号, 计数 器负责对  $A\Sigma$  调制器输出的数字脉冲进行计数,得到 一个转换周期里 🗚 🗅 调制器输出的脉冲个数, 因此计 数器的输出值就是该转换时间内温度的对应值,控制 时钟模块负责将外部输入时钟信号转换为系统工作所 需要的时钟信号,并为保护系统提供所需复位信号,偏 置和基准模块用于提供系统所需要的偏置电流和偏置 电压, 并为  $A \Sigma$  调制器的 A/D 转换器提供正负的基准 电压. 接口模块负责芯片和外部电路的通讯工作, 它在 每个转换周期结束的时候读取计数器中的计数值,并 送给外部电路进行处理.

本文设计了一种应用于温度传感器芯片的全差分 开关电容积分器,它是  $\Delta\Sigma$  调制器中最核心的元件,

图 1 温度传感器芯片总体框图

Fig. 1 Temperature sense IC architecture

把接收到的温度传感器模块输出的模拟信号转换为数字信号. 在设计过程中, 开关电容积分器存在 MOS 开关的导通电阻和电荷注入、时钟溃通、采样尖峰等非理想因素。本文对这些非理想因素做了详细的分析, 设计了一种全差分的开关电容积分器, 可以抵消开关电容中注入电荷和时钟溃通带来的电压误差. 同时, 本文设计了一种全差分共源共栅放大器, 具有足够大的直流增益和单位增益带宽, 可以很好地满足积分器的要求, 从而提高整个系统的性能.

## **1** △∑调制器的组成和基本原理

AΣ调制器的设计是 A/D 转换器获得高精度数据转换和较高信号带宽的关键。调制器的创新在于采用全差分电路结构、开关电容积分器以及过采样技术。全差分电路结构可以有效的减少谐波失真,抑制衬底理全隔点,开关电容和分器通过电容比值,获得精确的

收稿日期: 2006-1114

图 2 4 3 调制器方框图

Fig. 2 Functional diagram of a ΔΣA/D modulator

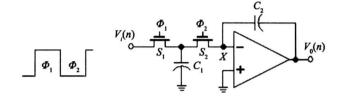

时间常数,提高积分器的精度.过采样是以远远大于信 号 Nyquist 采样频率的时钟对输入信号进行采样, 使 输出的数字信号在信号带宽内是高信噪比的, 调制器 的基本结构如图 2 所示, 它主要由积分器, 比较器和 A/D 转换器组成.

## 开关电容积分器

#### 2.1 开关电容积分器的基本原理

开关电容积分器是  $\triangle \Sigma A/D$  调制器的核心部分, 它是用开关和电容来代替有源 RC 网络中的电阻. 电 容值的精确程度比电阻阻值要容易控制, 控制时钟的 周期也很好控制, 开关电容可以得到精度很高的时间 常数. 开关电容积分器的基本结构如图 3 所示, Ф. Ф 为两相不交叠时钟,  $\Phi$  为采样相,  $\Phi$  为积分相,  $C_1$  为 采样电容.  $C_2$  为积分电容. 在每个时钟周期内. 当 $S_1$  导 通时,  $C_1$  吸收的电荷量等于  $C_1V_{in}$ ; 当  $S_2$  导通时, 由于 节点 X 为虚地点,  $C_1$  上的电荷转移到  $C_2$  上, 所以积分 器输出如式(1) 所示. 每个周期的电压增益为 $\frac{C_1}{C_2}^{(2)}$ .

$$V_{\text{out}}(nT) = V_{\text{out}}[(n-1)T] - V_{\text{in}}[(n-1)T] \frac{C_1}{C_2}$$

$$\tag{1}$$

#### 2, 2 开关电容积分器的非理想因素

#### 1) M OS 管的导通电阻的影响

由于MOS管开关并非理想开关、导通时的电阻非 零, 它与采样电容形成 RC 回路, 会影响电容的充放电 时间,如果导通电阻太大,就会造成系统的建立不完全 等问题, 另外, 导通电阻还是  $V_{\rm cs}$  的函数, 因此会对系 统造成一定的非线性误差.

为了减小MOS管导通电阻的影响,可以选用宽长 比较大的 MOS 管开关或采用 CMOS 开关.

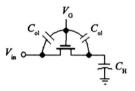

#### 2) 时钟馈通及采样尖峰

如图 4 所示, MOS 器件的栅源和栅漏极存在着寄 生的交叠电容. 当开关导通( $V_G$  为高电平) 时,  $C_H$  本来 应被充电到  $V_{\rm in}$ . 但交叠电容会将时钟低电平耦合到了 C<sup>H</sup> 上.产生误差电压:

$$\Delta V_{\text{out}} = V_{\text{G}} \frac{C_{\text{gd}}}{C_{\text{gd}}} \tag{2}$$

#### 图 3 开关电容积分器

Switched-capacitor integrator Fig. 3

MOS 管交叠电容示意图

Fig. 4 Diagram of parasitic capacitances

时钟馈通引起的另一干扰就是采样过程中出现的 电压尖峰. 由于开关的时钟的变化很快, 因此快速变化 的  $V_{\rm G}$  会通过 M OS 管的交叠电容耦合到漏极和源极. 根据公式  $i = C \frac{dU}{dt}$ , 将会在很短的时间内产生很大的 电流, 该电流流经电容和开关(电阻) 就会产生电压尖 峰, 这些电压尖峰将会通过积分器积累到输出端, 影响 积分器的精度.

为了减小时钟馈通和采样尖峰的影响, 可以采用 宽长比较小的 MOS 管, 以减小交叠电容,

#### 3) 电荷注入问题

当MOS管导通时,栅氧下的反型层中将积累一定 数量的电荷, 而当 MOS 管截止时, 沟道中所储存的电 荷就会从 MOS 管的源极和漏极流出, 这种现象称为 "沟道电荷注入", 流出的沟道电荷会存储在电容器上, 对电容器上的电压产生一定的误差. 注入到源极和漏 极的电荷的多少与源漏的阻抗、电位和时钟的跳变时 间都有关系[3], 为了消除电荷注入问题, 可以采取以下 方法: (a) 在输出节点接一虚拟 MOS 管; (b) 采用 CM OS 开关: (c) 采用非重叠时钟控制开关: (d) 采用 全差动结构的积分器,使两输入端的电荷注入影响相 抵消.

#### 4) 放大器特性问题

放大器对积分器的影响主要是由放大器的非理想 特性造成的, 其有限增益、转换速率和有限单位增益带 宽都会直接影响积分器的速度和精度,在实际设计中 要根据要求,设计性能较好的放大器.

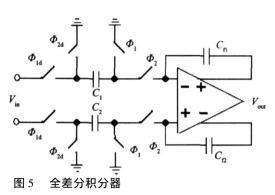

## 全差分开关电容积分器

Fig. 5 Fully differential switched capacitor integrator

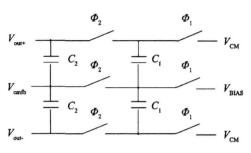

#### 3.1 全差分开关电容积分器的设计

基于以上分析, 本设计选用了如图 5 所示的全差分结构的开关电容积分器. 全差分结构可以抵消开关电容中注入电荷和时钟溃通带来的电压误差. 在时钟信号  $\Phi$  阶段, 电容  $C_1$  对输入信号采样;  $\Phi$  阶段, 电路进行积分运算.  $\Phi$ ,  $\Phi$  稍微先于  $\Phi$ d 和  $\Phi$ d, 从而减小由电荷注入引起的谐波失真. 图中的开关选用 CM OS 开关,可以消除 M OS 开关导通电阻的影响.

### 3.2 全差分运算放大器的设计

#### 1) 全差分 CMOS 运算放大器结构

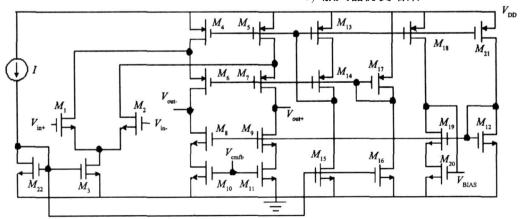

全差分运算放大器是全差分积分器实现的关键, 其有限增益、转换速率和有限单位增益带宽都会直接 影响积分器的速度和精度. 本设计选用了折叠式全差分放大器, 它具有较高的直流开环增益, 快速地建立时间和大的输出摆幅, 可以很好地满足积分器的要求.

图 6 为本文所设计的全差动折叠式共源共栅放大器, $M_1$ 、 $M_2$  为差分输入, $M_4 \sim M_7$  为输出级电路, $M_8 \sim M_{11}$  为输出级有源负载. 共模反馈(CMFB) 是通过控制  $M_{10}$  和  $M_{11}$  的偏置电压来实现. 要想获得较高的电压增益,可以提高输入级跨导,加大输出级  $M_6$ 、 $M_7$ 的输出阻抗. 并增大有源负载的输出阻抗.  $M_{12} \sim M_{21}$

图 7 共模反馈电路

Fig. 7 CMFB circuit

为低压共源共栅结构的偏置电路, 它为折叠式运算放大器提供了偏置电压. 这种结构可以减小电压余度的消耗, 增大输出摆幅.  $V_{\text{emfb}}$  和  $V_{\text{BAS}}$  分别和共模反馈网络相接, 偏置器件 $M_{19}$ 、 $M_{20}$  与放大器中器件 $M_{8} \sim M_{11}$ 相似以保证好的匹配.

#### 2) 共模反馈结构

同单端运放相比,全差分运放有很强的噪声抑制能力,缺点是需要共模反馈(CMFB)电路<sup>4]</sup>.对于全差分运算放大器,如果没有必要的控制,输出共模电压会因为电源电压变化、工艺变化和失调等因素而移向电源电压.加入CMFB电路,可以形成共模负反馈回路,控制共模输入电平的变化.只要共模反馈回路的带宽足够大,可以稳定快速的共模输入电平变化,共模输出电压就可以稳定在某一确定的值.本设计采用图 7 所示的开关电容 CMFB 电路结构.

在图 7 所示的电路中,  $V_{\text{CM}}$  是期望的共模输出电压,  $V_{\text{BIAS}}$  为一个偏置电压, 由  $M_{19}$  、 $M_{20}$  支路偏置确定, 当反馈至  $M_{10}$  、 $M_{11}$  的栅级电压  $V_{\text{cmfb}} = V_{\text{BIAS}}$  时, 输出共模电压等于所期望的共模输出电压. 为了达到最大的输出摆幅, 一般情况下令  $V_{\text{CM}} = \frac{1}{2}(V_{\text{dd}} + V_{\text{ss}})$ . 图 7 中所示的所有 NMOS 管用以实现开关功能.

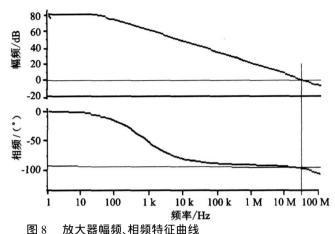

#### 3) 放大器仿真结果

图 6 全差动折叠式共源共栅放大器

Fig. 6 Fully differential folded-cascode operational amplifier

图 8 放入器幅测、相测符征曲线

图 8 为放大器的幅频、相频曲线, 系统在频率 40 MHz 附近足够稳定, 其直流增益可以达到 81.2 dB. 可以看出, 此放大器具有足够大的直流增益和单位增益带宽, 可以很好的满足积分器性能指标.

Gain and phase response of OP

### 3.3 时钟产生电路

Fig. 8

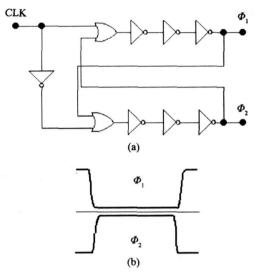

时钟发生电路是控制开关电容电路工作的重要的 电路模块,它们控制开关的时序,以减小电荷注入和时 钟溃通的影响.本设计采用两相不重叠时钟,用以控制 开关电容电路和共模反馈电路开关的时序.图 9 为两 相不重叠时钟脉冲发生器电路及其仿真结果.延时非 门的使用,使时钟间的非交叠特性更好.

## 4 积分器模拟结果

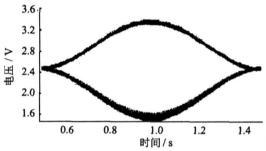

图 10 为输入为 10 kHz 的正弦信号的全差分开关电容积分器的 HSPICE 仿真结果. 其中采样电容  $C_1$ ,  $C_2$  为 0.5 pF, 积分电容  $C_{11}$ ,  $C_{12}$  为 1 pF. 开关的导通电阻约为 200  $\Omega$ , 时钟周期为 0.4  $\mu_s$ , 过采样率为 128. 从仿真结果可以看出, 积分器可以很好地对输入的正弦信号进行积分, 其输出结果经过比较器量化, 可以得到高精度的数字信号, 使调制器很好的满足系统的要求.

## 5 版图设计

本论文的主要工作是对开关电容电路积分器的设计.由开关电容电路积分器的分析可知,积分器的增益只与电容的比值有关,而与电容本身的值无关,因此要使开关电容电路具有较好的性能,必须精确地控制电容器的比值.

在 CMOS 工艺中制作电容器时误差产生的主要原因是刻蚀过度(即实际电容的面积小于版图掩膜的面积)和氧化层厚度梯度.因此,设计版图时,通过并联较小的单位面积电容来得到较大电容器的方法来减少

图 9 两相不重叠时钟发生器和仿真结果

(a) 发生器;(b)仿真结果

Fig. 9 Non-overlap clock driver and timing pulses

图 10 输入为 10 kHz 的正弦信号的输出结果

Fig. 10 Simulation result of 10 kHz sine input

刻蚀过度产生的误差,并采用与 MOS 管类似的"交叉 共心"布局来减小氧化层厚度梯度的误差.

## 6 结 论

本文设计了一种应用于温度传感器芯片的全差分开关电容积分器,并对 MOS 开关的导通电阻和电荷注入、时钟溃通、采样尖峰等非理想因素进行了系统的分析.折叠式全差分放大器,具有较高的直流开环增益和单位增益带宽,可以很好的满足积分器的要求.用两相不重叠时钟控制开关的时序,可以减小电荷注入和时钟溃通的影响.从仿真结果可以看出,所设计的积分器能很好地对输入信号进行积分,其输出信号经过比较器量化,可以输出高精度的数字信号,使调制器很好的满足整个系统的要求.

#### 参考文献:

[1] Anton Bakker. CMOS smart temperature sensors-An overview [J]. Proceeding of IEEE, 2002(2):1423-1427.

\*\*© 1994-2012で開稿 ACadeMe Yournal Electione Pablishing House. All rights reserved. http://www.cnki.net

- [2] Behazad Razavi. Design of analog CMOS integrated circuits M. New York: McGraw Hill, 2001.

- [3] Chen M J, Gu Y B, Wu T, et al. New observation of charge injection in MOS analogue switches[J]. Eelctron-

- ics Letters, 1994, 30(3): 213-214.

- [4] Phillip E Allen, Douglas R Holberg. CMOS analog circuit design[M]. New York: Publishing House of Electronics Industry, 2002.

# Design of a Fully Differential CMOS Switched capacitor Integrator for Temperature Sense IC

$\operatorname{GUO}$  Jian-ning, CHEN Wen-xiang  $^*$  , FENG Yong-jian

(Department of Mechanical and Electrical Engineering, Xiamen University, Xiamen 361005, China)

**Abstract:** A fully differential CMOS switched capacitor integrator for temperature sense IC is proposed and analyzed. In the temperature sense IC,  $\Delta \Sigma A/D$  modulator receives the voltage signal from the temperature sensor, and transforms the analog signal to digital signal. Fully differential CMOS switched capacitor integrator is the main part of the  $\Delta \Sigma A/D$  modulator. It can realize to transform the analog signal received from the temperature sensor to digital. In the practical design process, there are some non-ideal elements with switched capacitor integrator, such as non-zero Ron, charge injection error, sampling spike and clock feed through, etc. All of these non-ideal elements were analyzed in this paper and a fully differential was then presented, which can reduce the charge injection error of MOS switches, clock feed through and non-ideal performance of operational amplifier. The realization of fully differential folded cascode operational amplifier can improve the performance of the integrator by which the high performance of the whole system can be achieved.

Key words: temperature sense; fully differential CMOS switched capacitor integrator;  $\Delta \Sigma A/D$  modulator; fully differential folded-cascode operational amplifier