ELSEVIER

Contents lists available at ScienceDirect

### Science Bulletin

journal homepage: www.elsevier.com/locate/scib

#### Article

## High-current MoS<sub>2</sub> transistors with non-planar gate configuration

Jun Lin<sup>a</sup>, Bin Wang<sup>a</sup>, Zhenyu Yang<sup>c</sup>, Guoli Li<sup>a</sup>, Xuming Zou<sup>a</sup>, Yang Chai<sup>b</sup>, Xingqiang Liu<sup>a,\*</sup>, Lei Liao<sup>a,d,\*</sup>

- <sup>a</sup> Key Laboratory for Micro/Nano Optoelectronic Devices of Ministry of Education & Hunan Provincial Key Laboratory of Low-Dimensional Structural Physics and Devices, School of Physics and Electronics, Hunan University, Changsha 410082, China

- <sup>b</sup> Department of Applied Physics, The Hong Kong Polytechnic University, Hong Kong, China

- <sup>c</sup> College of Microtechnology & Nanotechnology, Qingdao University, Qingdao 266071, China

- <sup>d</sup> State Key Laboratory for Chemo/Biosensing and Chemometrics, School of Physics and Electronics, Hunan University, Changsha 410082, China

#### ARTICLE INFO

# Article history: Received 15 September 2020 Received in revised form 22 October 2020 Accepted 26 November 2020 Available online 9 December 2020

Keywords: MoS<sub>2</sub> transistors Omega-shaped gate Non-planar High current density

#### ABSTRACT

The ever-decreasing size of transistors requires effectively electrostatic control over ultra-thin semiconductor body. Rational design of the gate configuration can fully persevere the intrinsic property of two-dimensional (2D) semiconductors. Here we design and demonstrate a 2D  $MoS_2$  transistor with omega-shaped gate, in which the local gate coupling is enhanced by the non-planar geometry. The omega-shaped non-planar transistors exhibit a high current of 0.89 A/ $\mu$ m and transconductance of 32.7  $\mu$ S/ $\mu$ m. The high performance and desirable current saturation promise the construction of robust logic gate. The inverters show a voltage gain of 26.6 and an ideal total margin nearly 89%. We also assemble NOT-AND (NAND) gate on an individual  $MoS_2$  flake, and the constructed NAND gate demonstrates the universal functionality of the transistors as well. This work provides an alternative strategy to fully take the advantages of 2D materials for high-performance field-effect transistors.

© 2020 Science China Press. Published by Elsevier B.V. and Science China Press. All rights reserved.

#### 1. Introduction

Non-planar gate architecture promises an effective strategy for gate controllability enhancement because of excellent electrostatic control, which shows much better performance beyond conventional planar bulk technologies [1,2]. This structure offers the possibility for suppressing the short-channel effects with steep subthreshold swing (SS) as the continuously down scaling of transistors [3-5]. A wrap-around gate structure provides superior electrostatic gate control compared to planar structures [6,7]. As a consequence, the leakage current can then be suppressed while the device performance is still augmented. However, it requires complicated fabrication processes [8]. Namely, there is a compromise between the improvement in the electrostatic controllability and the fabrication complexity. An alternative solution to maximize the electrostatic confinement while minimizing the manufacturing complexity is to use an omega-shaped gate architecture, which possesses excellent electrical performance that induced by the improved gate controllability [2,9,10]. In the non-planar omega-shaped gate configuration, the semiconducting surface surrounded by the gate is increased in relation to the channel volume. The improvement of the electrostatic control offers low leakage

and low power consumption for the field-effect transistors with ultra-short channel length  $(L_{ch})$  [9]. However, 5 nm node silicon transistors require sub-3 nm body thickness for desirable channel control [11]. Traditional semiconductors are restricted by the mobility or quantum capacitance challenges at such ultra-thin body thickness. The imperfections of the traditional channel material surface scatter charge carriers, resulting in inferior current flow [12]. Moreover, the source-to-drain quantum tunneling or variability is pronounced and deteriorates the on-off ratio in scaled devices [13,14]. On the other hand, it is promising to apply other potential materials instead of silicon while scaling down the channel length of transistors [15–17]. Two-dimensional (2D) materials are crystalline sheets with atomic thickness. Due to the flat surfaces without dangling bonds, carriers are less prone to scattering and can flow relatively freely through the channel [18,19]. Therefore, 2D materials, such as MoS<sub>2</sub>, represent the ultimately scaled transistors in large-area electronics [20]. Previously reported works mainly focus on shortening the planner dimension for ultra-short channel length, which demonstrates superior on-state channel current and verifies the competitive performance with that of the silicon-based transistors in some aspect. However, the reported planar MoS2 field-effect transistors lack rational gatecoupling design, thus suffering from insufficient electrical performance [21-23].

In this work, non-planar MoS<sub>2</sub> field-effect transistors with omega-shaped gate configuration are fabricated. With the

<sup>\*</sup> Corresponding authors. E-mail addresses: liuxq@hnu.edu.cn (X. Liu), liaolei@whu.edu.cn (L. Liao).

enhanced electrostatic coupling from the rational design of gate configuration, the transistors demonstrate robust performance with a high current of 0.89 mA/ $\mu$ m, high on–off ratio of  $10^7$  and a low threshold voltage ( $V_{TH}$ ) of -2.85 V. Based on the excellent pinch-off and current saturation of the MoS $_2$  transistors, the NOT gate and NOT-AND (NAND) gate circuits are entirely assembled on an individual MoS $_2$  flake. The NOT gate inverters demonstrate a voltage gain of 26.6 at an applied voltage ( $V_{DD}$ ) of 4.5 V and an almost ideal noise margin approaching 0.5 $V_{DD}$ . And the constructed NAND gate indicates the universal functionality of the transistors. The strategy indicates a representative gate geometry design towards 2D electronics with competitive performance of silicon-based transistors.

#### 2. Experimental

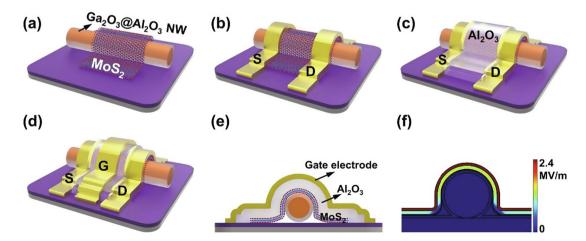

Few-layered MoS<sub>2</sub> can provide a balance between mobility and contact resistance of the device. Therefore, we adopt ~5 layers MoS<sub>2</sub> flakes as the channel layer in this work [24]. Fig. 1 schematically depicts fabrication process flow of our designed non-planar gate transistor. Firstly, the Ga<sub>2</sub>O<sub>3</sub> nanowires (NWs) are prepared in a single zone horizontal tube furnace with chemical vapor deposition, which is similar with the previously reported works [25,26]. The Ga<sub>2</sub>O<sub>3</sub> NW (the dimension D<sub>NW</sub> ranges from 60 to 300 nm, Fig. S1 online) with Al<sub>2</sub>O<sub>3</sub> dielectric layer was transferred onto 300 nm SiO<sub>2</sub> coated Si substrates, in which the Al<sub>2</sub>O<sub>3</sub> dielectric layer is deposited via atomic layer deposition (ALD) approach [24]. And then the MoS<sub>2</sub> flake was transferred onto the nanowire by a physical dry transfer process [27]. Subsequently, ethyl alcohol was dipped onto the substrate and dried in air naturally to ensure the intimate contact between NW and MoS2 flakes. The number of MoS<sub>2</sub> layers was confirmed by atomic force microscope image in Fig. S2 (online). Raman spectra based on the peak spacing between the E1 2g mode and the A<sub>1g</sub> mode (Fig. S3 online), and the Raman spectra of the MoS<sub>2</sub> onto the Ga<sub>2</sub>O<sub>3</sub> nanowire also present the consistent characteristic peak with that of the MoS<sub>2</sub> onto the SiO<sub>2</sub> substrate, indicating the strain is nearly released. The external source/ drain region was defined by e-beam lithography, and Cr/Au electrode with a thickness of 10 nm/70 nm was deposited by thermal evaporator followed by the lift-off process, as shown in Fig. 1b [28]. ALD was employed to fabricate 15 nm top-gated Al<sub>2</sub>O<sub>3</sub> dielectric, as shown in Fig. 1c. Fig. 1d is the schematic image of the fabricated omega-shaped gate  $MoS_2$  transistor, in which the top gate Cr/Au electrode (10 nm/70 nm) was fabricated by beam lithography (EBL) followed by metal deposition and lift-off process. Fig. 1e is the cross-sectional schematic image of the gate architecture of the omega-shaped gate  $MoS_2$  transistor. To reveal the effect of the gate configuration, finite element simulation was carried out by COMSOL Multiphysics. Fig. 1f is the corresponding finite element simulation of the electric field of the top gate. 2D model was created based on the structure of the fabricated device, and the electric field distribution was obtained by Semiconductor Module. The results indicate that the local electric field strength is enhanced by the non-planar gate configuration. The total top-gate capacitance (including simulated electrostatic capacitance and quantum capacitance) is calculated using electrostatic module and normalized by  $MoS_2$  channel area, which is about  $308.5 \text{ nF/cm}^2$ .

#### 3. Results and discussions

#### 3.1. Electrical performance of the omega-shaped gate MoS<sub>2</sub> transistors

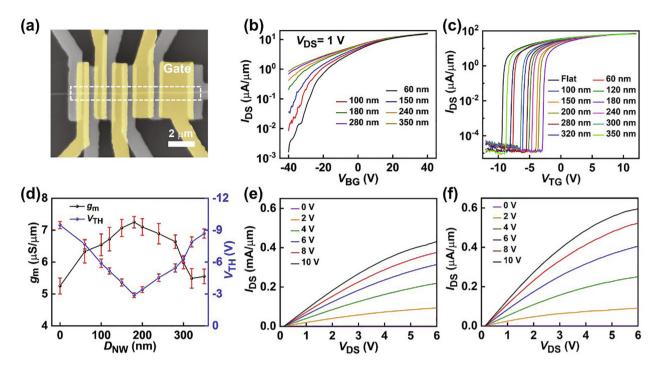

Fig. 2a is the scanning electron microscope (SEM) image of the top view of the omega-shaped gate MoS2 transistors with channel length ( $L_{CH}$ ) ranging from 150 nm to 2  $\mu$ m. Fig. 2b shows typical transfer curves of the back-gated MoS2 transistors with different buried  $D_{NW}$ , and  $D_{NW}$  is approximately equal to two times of the bending radius. As partial channel is separated by the nanowire from the back gate, the electrostatic coupling of the back gate is weakened for the devices with even larger  $D_{NW}$ . Therefore, the on-off ratio decreases with the increase of  $D_{NW}$ , which originates from the increased off-state current and decreased on-state current at larger  $D_{NW}$ . Fig. 2c is the evolution of the transfer characteristics of the omega-shaped gate MoS<sub>2</sub> transistors versus D<sub>NW</sub>. All the devices present typical n-type characteristic with distinct pinch-off and an on-off ratio ~10<sup>7</sup>. Typical hysteresis transfer characteristic of the transistors is shown in Fig. S4 (online). Due to the traps in dielectric layer, the gate capacitance does not follow gate voltage sweeping, leading to the hysteresis. Fig. 2d plots the variations of the transconductance  $(g_m)$  and  $V_{TH}$  versus  $D_{NW}$ . As the local gate field is enhanced by the omega-shaped gate configuration with the support of the nanowire, the  $g_{\rm m}$  increases with  $D_{\rm NW}$  below 180 nm. The maximum field-effect mobility is calculated to be 47.2 cm<sup>2</sup>/(V s). Nevertheless, with the further increase of  $D_{NW}$ ,

**Fig. 1.** Schematic illustrations of the fabrication processes of the  $MoS_2$  transistors with omega-shaped gate. (a) Few-layer  $MoS_2$  flake is transferred onto the  $Ga_2O_3$  NW with  $Al_2O_3$  dielectric layer, and etched with a fixed width of 1 μm. (b) The source/drain contact region is defined via e-beam lithography, Cr/Au (10 nm/70 nm) deposition with thermal evaporation and lift-off processes. (c)  $Al_2O_3$  top-gated dielectric layer with a thickness of 15 nm is deposited by ALD. (d) The top-gate electrode region is defined by e-beam lithography, Cr/Au (10 nm/70 nm) deposition and lift-off processes. (e) Cross-sectional schematic image of the transistor. (f) The electric field distribution in the gate confirmation.

**Fig. 2.** Electrical performance of the omega-shaped gate MoS<sub>2</sub> transistors. (a) SEM image of the top view of the omega-shaped gate MoS<sub>2</sub> transistors. (b) Typical back-gated transfer characteristics of the omega-shaped gate MoS<sub>2</sub> transistors with different  $D_{NW}$ . (c) Typical top-gated transfer characteristics of the omega-shaped gate MoS<sub>2</sub> transistors with different  $D_{NW}$ , and the  $V_{DS}$  = 1 V for all the curves. (d) The plots of  $g_m$  and  $V_{TH}$  versus  $D_{NW}$ , and the statistical data are captured from the devices with a variation range of ±10 nm for  $D_{NW}$ . (e, f) The output characteristics of the MoS<sub>2</sub> transistors with planar (e) and omega-shaped (f) gate configuration, respectively.

the shape of the gate is approaching to planar, leading to degraded electrical performance that similar to the planar ones. Similarly, the  $V_{\rm TH}$  of the devices is impacted by  $D_{\rm NW}$ , which is induced by the  $D_{\rm NW}$  dependent field distribution of the omega-shaped gate configuration [9,29]. Fig. 2e, f are the output curves of the MoS<sub>2</sub> transistors with planar and omega-shaped gate configuration ( $D_{\rm NW}$  = 180 nm), respectively. The obvious pinch-off characteristics suggest that the MoS<sub>2</sub> active channel is fully modulated by the gate voltage. The largest output current of the planar and omega-shaped gate MoS<sub>2</sub> transistors are 0.47 and 0.59 mA/ $\mu$ m, respectively. Benefiting from ultra-thin body, the large bandgap of 1.2 eV and enhanced electrostatic control, channel current saturation and turn off is observed. These results indicate the present strategy is feasibility for enhancing the electrical performance of the MoS<sub>2</sub> transistors.

# 3.2. Electrical reliability of the short-channel omega-shaped top-gated $MoS_2$ transistors

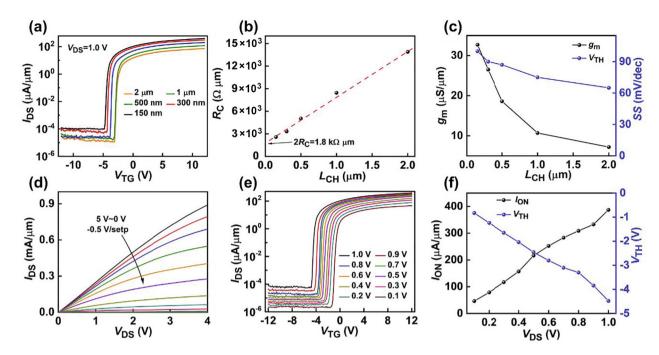

We also investigate short-channel omega-shaped gate MoS<sub>2</sub> transistors. We adopt the MoS<sub>2</sub> flakes with similar thickness onto the nanowire with similar dimension to ensure a reliable comparison between the devices data. Fig. 3a presents typical transfer characteristics of fabricated devices. As the channel length shrinks, the on-state current is gradually increasing. Due to the shortchannel effect (SCE), the devices obtain large  $V_{\rm TH}$  values to pinch off the active channel. Transfer length method is used to extract contact resistance [30-32]. Fig. 3b is the plots of total channel resistance ( $R_T$ ) as a function of channel length at  $V_{DS}$  = 1.0 V and  $V_{TG}$  = 12.0 V, which is the sum of two times of contact resistance  $(R_{\rm C})$  and channel resistance  $(R_{\rm CH})$ . The  $R_{\rm C}$  is about 0.9 k $\Omega$  µm under working condition, indicating that the contact resistance does not dominate the transport property of MoS2 devices. Fig. 3c plots the  $g_{\rm m}$  and SS versus  $L_{\rm CH}$ . The  $g_{\rm m}$  is increased as the channel length shrinks. In addition, the peak  $g_m$  of 32.7  $\mu S/\mu m$  obtained at

$V_{\rm DS}$  = 1.0 V is comparable with the previously reported values at a high  $V_{\rm DS}$  = 5.0 V [21]. And due to the enhanced gate electrostatic coupling from the omega-shaped gate configuration, the devices with different channel lengths present steep subthreshold characteristic with a SS below 100 mV/dec as  $L_{CH}$  = 150 nm. Fig. 3d is the output current of the omega-shaped top-gated MoS2 transistors with an  $L_{CH}$  = 150 nm. A maximum output current of 0.89 mA/ um is obtained, proving that the output current density has not been sacrificed for the diminution of  $L_{CH}$ . Table S1 (online) presents the performance comparisons among the MoS<sub>2</sub> transistors with similar channel length to state the significance of this work. And the current density of the MoS<sub>2</sub> is competitive with those in the previously reported work [33-35]. The sufficient current saturation in the omega-shaped top-gated MoS<sub>2</sub> transistors at short channel length is benefit for large voltage gain in circuits. Draininduced barrier lowering (DIBL) is a short-channel effect in transistors referring originally to a reduction of threshold voltage of the transistor at higher drain voltages, which is induced by the electrostatic shield from the  $V_{\rm DS}$  [36]. Fig. 3e is the transfer curves of the omega-shaped top-gated MoS<sub>2</sub> transistors with an  $L_{CH}$  = 150 nm. The residual leakage current in short channel devices as the  $V_{DS}$ is increased, and DIBL is 4.05 V for the devices with  $L_{\rm CH}$  = 150 nm. Fig. 3f indicates the linear increment of  $I_{ON}$  as the  $L_{CH}$  decreasing. As the electrostatic screening from the  $V_{\rm DS}$ , large  $V_{\rm TG}$  is needed to pinch off the channel, leading to large  $V_{\mathrm{TH}}$  values at high  $V_{\mathrm{DS}}$ . These results indicate that the MoS<sub>2</sub> transistors with omega-shaped gate configuration show good immunity to short channel effects and potential for high-performance logic gate [36.37].

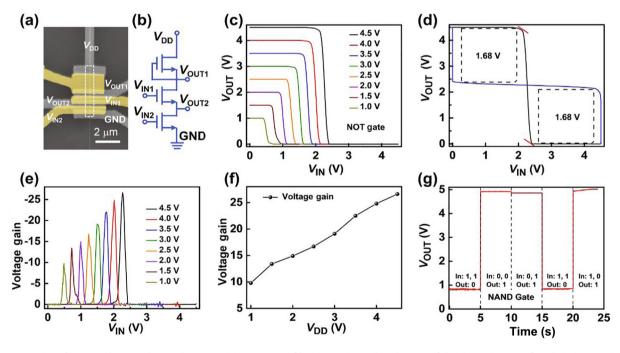

The direct-coupled field-effect transistor logic (DCFL) technology is a popular architecture for constructing low-power circuit [38]. As shown in Fig. 4a, in order to obtain high output current and transconductance, the gate region is fully over-lapping the channel, thus minimized parasitic and contact resistance can be persevered [23]. Fig. 4b is the corresponding circuit diagram of the fabricated devices. An inverter circuit is a basic logic element

**Fig. 3.** Electrical reliability of the short-channel omega-shaped top-gated MoS<sub>2</sub> transistors. (a) Transfer curves of the omega-shaped top-gated MoS<sub>2</sub> transistors with different channel lengths. (b) Total channel resistance as a function of channel length at  $V_{DS}$  = 1.0 V and  $V_{TG}$  = 12.0 V. (c) The dependence of  $L_{ch}$  on  $g_m$  and SS. (d) Typical output current of the omega-shaped top-gated MoS<sub>2</sub> transistors with an  $L_{CH}$  = 150 nm. (e) Semi-log plot of the transfer characteristics with  $L_{CH}$  = 150 nm at different  $V_{DS}$ . (f)  $L_{CH}$  dependent  $I_{ON}$  and  $V_{TH}$  of the omega-shaped top-gated MoS<sub>2</sub> transistors.

**Fig. 4.** Demonstration of integrated NOT and NAND logic gate. (a) SEM image of logic gate circuit. (b) Schematic of the electronic circuit for a logic inverter (when  $V_{OUT2}$  terminal is ground) and NAND (when  $V_{OUT2}$  terminal is suspending). (c) Output characteristics of the inverter at different  $V_{DD}$ . (d) Output voltage as a function of the input voltage and its mirror reflection. And noise margins (NM<sub>L</sub> = 0.45 $V_{DD}$ , NM<sub>H</sub> = 0.44 $V_{DD}$ ) of the inverter. (e) Corresponding voltage gain of the inverter at different  $V_{DD}$ . (f) Voltage gain as a function of  $V_{DD}$ . (g) Output voltage of the NAND gate at different input states: (1, 1), (0, 0), (0, 1), (1, 1) and (1, 0). A low voltage of 0.1 V represents a logic state 0 and a voltage of 5 V represents a logic state 1.

that outputs a voltage representing the opposite logic-level to its input. When  $V_{\rm OUT2}$  terminal is ground, it works as a logic inverter. And when  $V_{\rm OUT2}$  terminal is suspending without any power connection, a NAND gate is constructed. Fig. 4c is the output characteristics of the inverter at different  $V_{\rm DD}$ . The inverter exhibits sharp

transition between high and low level. The noise margin is the maximum voltage amplitude of extraneous signal that can be algebraically added to the noise-free worst-case input level without causing the output voltage to deviate from the allowable logic voltage level. As shown in Fig. 4d, the high noise margins (NM $_{\rm H}$ ) and

low–noise margins (NM<sub>L</sub>) are extracted from the voltage transfer characteristic and its mirror reflection curve, and NM<sub>L</sub> =  $0.45V_{\rm DD}$  and NM<sub>H</sub> =  $0.44V_{\rm DD}$  are obtained, indicating the robustness of the inverter towards noise. The inverter demonstrates a total margin nearly 89% and an almost ideal noise margin of 0.5 at  $V_{\rm DD}$  = 4.5 V. Fig. 4e is the voltage gain of the inverter that calculated by taking the derivation of the voltage transfer curves. Fig. 4f indicates the voltage gain increases with increasing  $V_{\rm DD}$  and a voltage gain 26.6 is achieved at  $V_{\rm DD}$  = 4.5 V. In Fig. 4g, the output voltage of the NAND gate is measured as a function of time while the two input voltage states vary across all four possible logic combinations (1,1), (0,0), (0,1) and (1,0). The results demonstrate robust NAND gate functions that constructed with the omega-shaped top-gated MoS<sub>2</sub> transistors.

#### 4. Conclusion

In summary, we mainly focus on enhancing the local gate field coupling of the  $MoS_2$  transistors by introducing an omega-shaped top-gated configuration. Owing to the improved gate controllability from the sharpened corner geometry, the top-gated devices exhibit good immunity to short channel effects, current saturation at short channel length, reliable operation. NOT and NAND gate with robust functions are constructed based on the desirable transistor performance, and the inverter indicates nearly ideal noise margins and high voltage gain. The strategy presents a rational design of the gate geometry and is an alternative avenue to promote high-performance low-power applications for 2D materials.

#### **Conflict of interest**

The authors declare that they have no conflict of interest.

#### Acknowledgments

This work was supported by the National Key Research and Development Program of China (2018YFA0703704 and 2018YFB0406603), China National Funds for Distinguished Young Scientists (61925403), the National Natural Science Foundation of China (61851403, 51872084, 61704052, 61811540408, and 61704051), the Strategic Priority Research Program of Chinese Academy of Sciences (XDB30000000), and in partly by the Key Research and Development Plan of Hunan Province (2018GK2064).

#### **Author contributions**

Xingqiang Liu and Lei Liao conceived and designed the experiments. Jun Lin prepared the manuscript. Bin Wang and Guoli Li finished numerical simulation related parts, and also contributed to analysis and interpretation of results. Zhenyu Yang fabricated the MoS<sub>2</sub> back-gated devices, and the related characterizations and measurements. Yang Chai and Xuming Zou presented the suggestions for improving the quality of this work and revised the manuscript. Top-gated devices related tests and result analysis were done by Jun Lin using protocols provided by Lei Liao. All authors examined and commented on the manuscript.

#### Appendix A. Supplementary materials

Supplementary materials to this article can be found online at https://doi.org/10.1016/j.scib.2020.12.009.

#### References

- [1] Jiang B, Yang Z, Liu X, et al. Interface engineering for two-dimensional semiconductor transistors. Nano Today 2019;25:122–34.

- [2] Zhao D-H, Tian Z-L, Liu H, et al. Realizing an omega-shaped gate MoS<sub>2</sub> field-effect transistor based on a SiO<sub>2</sub>/MoS<sub>2</sub> core-shell heterostructure. ACS Appl Mater Interfaces 2020;12:14308–14.

- [3] Wang F, Liu J, Huang W, et al. Subthermionic field-effect transistors with sub-5 nm gate lengths based on van der waals ferroelectric heterostructures. Sci Bull 2020:65:1444–50.

- [4] Xie Q, Lin X, Wang Y, et al. Performance comparisons between 7-nm FinFET and conventional bulk CMOS standard cell libraries. IEEE Trans Circuits Syst II 2015;62:761–5.

- [5] Xu M, Zhu H, Zhao L, et al. Improved short channel effect control in bulk FinFETs with vertical implantation to form self-aligned halo and punchthrough stop pocket. IEEE Electron Device Lett 2015;36:648–50.

- [6] Williams N, Silva H, Gokirmak A. Nanoscale ringFETs. IEEE Electron Device Lett 2012:33:1339–41.

- [7] Guerfi Y, Larrieu G. Vertical silicon nanowire field effect transistors with nanoscale gate-all-around. Nanoscale Res Lett 2016;11:210.

- [8] Saito T, Saraya T, Inukai T, et al. Suppression of short channel effect in triangular parallel wire channel MOSFETs. IEICE Transactions on Electron 2002;85:1073–8.

- [9] Barraud S, Coquand R, Casse M, et al. Performance of omega-shaped-gate silicon nanowire MOSFET with diameter down to 8 nm. IEEE Electron Device Lett 2012;33:1526–8.

- [10] Gaillardin M, Paillet P, Ferlet-Cavrois V, et al. High tolerance to total ionizing dose of Ω-shaped gate field-effect transistors. Appl Phys Lett 2006;88:223511.

- [11] Cheng R, Yin L, Wang F, et al. Van der Waals integration of 2D atomic crystals for advanced multifunctional devices. Sci Bull 2019;64:1033–5.

- [12] Cao W, Kang J, Sarkar D, et al. 2D semiconductor FETs—projections and design for sub-10 nm VLSI. IEEE Trans Electron Devices 2015;62:3459–69.

- [13] Liu L, Lu Y, Guo J. On monolayer MoS<sub>2</sub> field-effect transistors at the scaling limit. IEEE Trans Electron Devices 2013;60:4133–9.

- [14] Mishra V, Smith S, Liu L, et al. Screening in ultrashort (5 nm) channel MoS<sub>2</sub> transistors: a full-band quantum transport study. IEEE Trans Electron Devices 2015;62:2457–63.

- [15] Lv Y, Qin W, Wang C, et al. Recent advances in low-dimensional heterojunction-based tunnel field effect transistors. Adv Electron Mater 2019;5:1800569.

- [16] Yang Z, Liao L, Gong F, et al. WSe<sub>2</sub>/GeSe heterojunction photodiode with giant gate tunability. Nano Energy 2018;49:103–8.

- [17] Ye L, Li H, Chen Z, et al. Near-infrared photodetector based on MoS<sub>2</sub>/black phosphorus heterojunction. ACS Photonics 2016;3:692–9.

- [18] Li L, Yu Y, Ye GJ, et al. Black phosphorus field-effect transistors. Nat Nanotechnol 2014;9:372–7.

- [19] Radisavljevic B, Radenovic A, Brivio J, et al. Single-layer MoS<sub>2</sub> transistors. Nat Nanotechnol 2011;6:147–50.

- [20] Wang H, Yu L, Lee Y-H, et al. Integrated circuits based on bilayer MoS<sub>2</sub> transistors. Nano Lett 2012;12:4674–80.

- [21] Liu Y, Guo J, Wu Y, et al. Pushing the performance limit of sub-100 nm molybdenum disulfide transistors. Nano Lett 2016;16:6337–42.

- [22] Xu L, Gao N, Zhang Z, et al. Lowering interface state density in carbon nanotube thin film transistors through using stacked Y<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> gate dielectric. Appl Phys Lett 2018;113:083105.

- [23] Liao L, Zou X. Interface engineering for high-performance top-gated MoS<sub>2</sub> field effect transistors. In: Proceedings of the IEEE International Conference on Solid State and Integrated Circuit Technology, 2014.

- [24] Liu X, Yang X, Gao G, et al. Enhancing photoresponsivity of self-aligned MoS<sub>2</sub> field-effect transistors by piezo-phototronic effect from GaN nanowires. ACS Nano 2016;10:7451–7.

- [25] Liu X, Liu XI, Wang J, et al. Transparent, high-performance thin-film transistors with an ingazno/aligned-SnS<sub>2</sub>-nanowire composite and their application in photodetectors. Adv Mater 2014;26:7399–404.

- [26] Zou X, Liu X, Wang C, et al. Controllable electrical properties of metal-doped In<sub>2</sub>O<sub>3</sub> nanowires for high-performance enhancement-mode transistors. ACS Nano 2013;7:804–10.

- [27] Li H, Li X, Park J-H, et al. Restoring the photovoltaic effect in graphene-based van der Waals heterojunctions towards self-powered high-detectivity photodetectors. Nano Energy 2019;57:214–21.

- [28] Song W, Li YI, Zhang K, et al. Steep subthreshold swing in gaN negative capacitance field-effect transistors. IEEE Trans Electron Devices 2019;66:4148-50.

- [29] Chen M, Lin C, Kai-Hsin L, et al. Hybrid Si/TMD 2D electronic double channels fabricated using solid CVD few-layer-MoS<sub>2</sub> stacking for Vth matching and CMOS-compatible 3DFETs. In: Proceedings of the 2014 IEEE International Electron Devices Meeting, 15-17 Dec. 2014, 2014.

- [30] Du Y, Liu H, Deng Y, et al. Device perspective for black phosphorus field-effect transistors: contact resistance, ambipolar behavior, and scaling. ACS Nano 2014;8:10035–42.

- [31] Xia F, Perebeinos V, Lin Y-M, et al. The origins and limits of metal-graphene junction resistance. Nat Nanotechnol 2011;6:179–84.

- [32] Kaushik N, Nipane A, Basheer F, et al. Schottky barrier heights for Au and Pd contacts to MoS<sub>2</sub>. Appl Phys Lett 2014;105:113505.

[33] Liu X, Liang R, Gao G, et al. MoS<sub>2</sub> negative-capacitance field-effect transistors with subthreshold swing below the physics limit. Adv Mater 2018:30:1800932.

- [34] Liu X, Liu Y, Chen W, et al. Ferroelectric memory based on nanostructures. Nanoscale Res Lett 2012;7:285.

- [35] Appleby DJ, Ponon NK, Kwa KS, et al. Experimental observation of negative capacitance in ferroelectrics at room temperature. Nano Lett 2014;14:3864–8.

- [36] Das S, Chen H-Y, Penumatcha AV, et al. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. Nano Lett 2013;13:100–5.

- [37] Cheng R, Jiang S, Chen Y, et al. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat Commun 2014;5:5143.

- [38] Wang L, Chen L, Wong SL, et al. Electronic devices and circuits based on waferscale polycrystalline monolayer MoS<sub>2</sub> by chemical Vapor deposition. Adv Electron Mater 2019;5:1900393.

Xingqiang Liu is an associate professor of Electronic Science and Technology, Hunan University. He received his Ph.D. degree in Physics from Wuhan University in 2015. He joined the School of Electronics and Science, Hunan University in 2016. His research involves design of high-performance low-power electronics.

Lin Jun is currently a Ph.D. student under the supervisor of Prof. Lei Liao. He joined the School of Electronics and Science, Hunan University in 2015. His current research interest focuses on fabricating transistors with steep subthreshold swing.

Lei Liao is a professor of Electronic Science and Technology, Hunan University. He received his Ph.D. degree in Physics from Wuhan University in 2009. He was a professor of Wuhan University before joining Hunan University in 2016. His research involves design and synthesis of lowdimensional materials and processing methods for highperformance electronics.