技

葛 达 <sup>1,2</sup> 梁福田 <sup>1</sup> 王鑫喆 <sup>1</sup> 冯 博 <sup>1</sup> 朱宇龙 <sup>1</sup> 朱晨曦 <sup>1</sup> 陈 炼 <sup>1</sup> 李 锋 <sup>1</sup> 尚爱国 <sup>2</sup> 金 革 <sup>1</sup>

1 (中国科学技术大学 核探测与核电子学国家重点实验室 合肥 230026) 2 (中国人民解放军火箭军工程大学 西安 710025)

摘要 针对高能物理实验中飞行时间探测器的时间测量高精度需求,基于 0.13 μm 互补金属氧化物半导体 (Complementary Metal Oxide Semiconductor, CMOS)工艺设计了一种可应用在时间内插法中作为细计数模块的 单周期时间数字转换器(Time to Digital Convertor, TDC),并为测试设计了一个闭环测试系统。通过实测数据分 析,在相同的条件下设计对比试验,寻找 TDC 刻度非均匀性的来源,并给出相应的校准方法。测试结果表明: 校准后 TDC 的分辨率达到 57 ps, 精度好于 40 ps, 达到了预期的设计目标。

关键词 专用集成电路,时间数字转换器,闭环测试系统,对比实验

中图分类号 TL824

**DOI:** 10.11889/j.0253-3219.2018.hjs.41.040401

# Design and test of time-interpolation TDC based on 0.13 µm CMOS process

GE Da<sup>1,2</sup> LIANG Futian<sup>1</sup> WANG Xinzhe<sup>1</sup> FENG Bo<sup>1</sup> ZHU Yulong<sup>1</sup> CHEN Lian<sup>1</sup> LI Feng<sup>1</sup> SHANG Aiguo<sup>2</sup> JIN Ge<sup>1</sup>

1(State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei 230026, China) 2(Rocket Force University of Engineer, The Chinese People's Liberation Army, Xi'an 710025, China)

**Abstract** [Background] Time-of-flight measurement is a basic method to identify charged particles in high-energy physics experiments. [Purpose] This paper aims to realize time measurement resolution of flight time detectors in high-energy physics experiments within 50 ps. [Methods] Based on the 0.13 μm complementary metal oxide semiconductor (CMOS) process, we designed a single-cycle time to digital convertor (TDC) as a fine counting module in time interpolation and built a closed-loop test system. [Results] Through analysis of measured data, we designed the comparison test under the same conditions, and found the source of TDC scale heterogeneity, and proposed the corresponding calibration method. [Conclusion] The resolution of TDC after calibration is up to 57 ps and the accuracy is better than 40 ps.

**Key words** Application-specific integrated circuit, TDC, Closed-loop test system, Comparison test

国家自然科学基金(No.61401422)资助

第一作者: 葛达, 男, 1994年出生, 2015年毕业于火箭军工程大学, 现为硕士研究生, 研究方向为核辐射探测与核电子学技术

通信作者: 梁福田, E-mail: ftliang@ustc.edu.cn

收稿日期: 2017-06-16, 修回日期: 2017-10-20

Supported by National Natural Science Foundation of China (No.61401422)

First author: GE Da, male, born in 1994, graduated from Rocket Force University of Engineer in 2015, master student, focusing on nuclear radiation detection and nuclear electronics

Corresponding author: LIANG Futian, E-mail: ftliang@ustc.edu.cn

Received date: 2017-06-16, revised date: 2017-10-20

040401-1

在高能物理实验中,飞行时间探测器通过测量粒子的飞行时间来实现粒子鉴别。为了实现较好的粒子分辨能力,对时间的分辨能力要求达到百 ps量级以内<sup>[1]</sup>,需要高精度的时间数字转换器(Time to Digital Convertor, TDC)。

ASIC (Application Specific Integrated Circuit)技术使用用户全定制或半定制的电路,可以根据用户需要设计信号传播路径,一旦芯片制作成功,信号的路径延迟固定不变,不会受到综合和局部布线的影响,所以在大型科学研究和科学实验中应用较多<sup>[2-7]</sup>。

本文基于 0.13 μm 互补金属氧化物半导体 (Complementary Metal Oxide Semiconductor, CMOS) 工艺进行 TDC 的设计,根据高能物理实验中百 ps 量级以内的时间分辨率要求,预期最终达到 50 ps 以内精度的目标。

# 1 时间内插法的基本原理

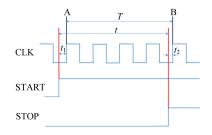

时间测量最简单易行的方法是用计数器对系统 时钟进行计数。这种方式的精度受限于系统时钟周 期,通常为 ns 量级,为了实现比时钟周期更小的测 量精度,需要对时钟进行插值。如图1所示,整个 时间测量系统由两个细计数 TDC 和一个粗计数器 组成, START 和 STOP 是两路随机的输入信号, CLK 是系统的时钟信号。待测的时间t是START和STOP 信号上升沿之间的时间间隔,一个细计数 TDC 记录 输入信号 START 上升沿与随后的 CLK 上升沿 A 之 间的时间间隔 t<sub>1</sub>,另一个细计数 TDC 记录输入信号 STOP 上升沿与随后的 CLK 上升沿 B 之间的时间间 隔 t<sub>2</sub>,粗计数器记录 START 上升沿和 STOP 上升沿 之间时钟周期的个数。将细计数 TDC 的量程设计成 稍长于 CLK 的一个时钟周期,则可以实现粗计数与 细计数的连接。由图 1 可见,所需测量的 START 信号与 STOP 信号之间的时间间隔 t 为:

$$t = T + t_1 - t_2 \tag{1}$$

图 1 时间间隔测量 Fig.1 Diagram of time interval measurement

# 2 TDC 及其测试系统设计

通过以上描述可知,使用时间内插法进行时间测量,其精度主要由细计数部分决定。本文主要设计和探讨在时间内插法中作为细计数模块的单周期TDC,粗计数部分可通过与计数器配合实现,本文将不再赘述。

# 2.1 TDC 的 ASIC 实现

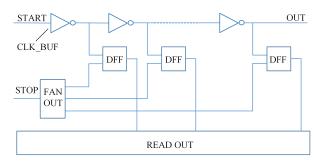

作为精细时间测量,本文选用时钟缓冲(CLK\_BUF)作为最小的延时单元,将CLK\_BUF 串联成信号延时链,让开始信号(START)在延时链中传递,当停止信号(STOP)到达时,通过对称树式扇出(FAN OUT),利用 STOP 信号,锁存所有CLK\_BUF的状态。然后利用读出结构(READ OUT)将 START 信号在延时链上的位置信息读出,通过分析即可得出 TDC 中 START 与 STOP 信号的时间之差。整体结构如图 2 所示。

图 2 TDC 结构 Fig.2 Diagram of TDC structure

显然 TDC 的性能很大程度上取决于延时单元链的均匀性,为确保各延时单元的延迟时间高度一致,本文在进行 ASIC 设计时对延时单元链部分采用纯模拟流程的手工布线。本次 TDC 共设计 64 个延时单元(64 Bin)。对延时链的时延进行带寄生参数的后仿真,64 Bin 对应总延迟时间为 3.753 ns,平均每 Bin 约 58 ps。

#### 2.2 测试系统的设计

TDC 设计完成后,对其精度等性能指标进行测试。测试选用 Agilent 81150A 脉冲函数任意噪声发生器做输入信号源(Signal Source),它的耦合模式可以保证两个通道的延时固定,延时可调范围可以精确到 1 ps,满足测试需求。

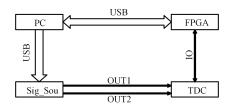

此外,测试需要一个控制模块对 TDC 的状态和信号源的参数设置进行控制,同时采集 TDC 读取的数据并将读到的温度计码转码为十进制数。本文基于 LabVIEW 对上位机(PC)进行软件设计,利用上

040401-2

位机与现场可编程门阵列(Field-Programmable Gate Array, FPGA)及信号发生器的通信搭建了一个闭环测试系统。上位机通过 LabVIEW 的虚拟仪器软件架构(Virtual Instrument Software Architecture)对信号源进行控制,将信号源两路信号输出的波形和延时等参数设定为测试所需的状态。设定好信号源的输出之后,需要对 TDC 的状态位进行写的操作,并给出时钟信号读取 TDC 测到的数据,以及对读取的数据进行处理,本系统选用一个 FPGA 来实现以上的数据读写和处理功能。为了实现上位机与 FPGA的通信,加入一个通用串行总线(Universal Serial Bus, USB)接口芯片,上位机通过 LabVIEW 的虚拟仪器软件架构与 FPGA 进行 USB 通信,由此构成一个整体的闭环测试结构,图 3 为其结构示意图,图 4 为其实物图。

图 3 测试系统结构 Fig.3 Diagram of test system structure

图 4 测试系统实物图 Fig.4 Actual picture of test system

### 3 TDC 的刻度标定

上位机控制信号源两个通道在耦合模式下输出OUT1和OUT2分别作为START信号和STOP信号。设置OUT1的延迟时间为0ps;设置OUT2的延迟时间从0ps开始,每次步进1ps直到TDC的量程3.2ns。上位机在设置好OUT2的延迟时间后,发送命令给FPGA,控制其将相应状态位写入TDC,进行读数并完成转码和储存。对每个设置的延迟时间进行500次测试,统计TDC读数,按照TDC每个

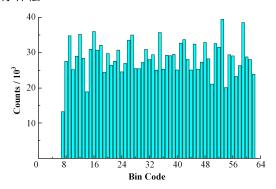

读数为一个时间 Bin 宽,得到统计结果如图 5 所示。 (图 5 中前几 Bin 没有计数的原因是 STOP 信号的 传输本身存在一定延迟)。

虽然 TDC 设计时严格控制时间延时 Bin 宽一致,但上述结果显示各延迟单元的计数并不均匀。 为了提升 TDC 的性能,需要分析延迟链均匀性缺失的原因以改善 TDC 的设计并利用刻度修正的方法进行补偿。

图 5 TDC 各延迟单元的计数 Fig.5 Counts of TDC delay bin

分析其各延迟单元计数不均匀原因存在两种可能:一是芯片在刻蚀加工时出现了一些不可避免的偏差,导致在延迟链上产生了分布不均匀的寄生参数,从而破坏了延迟链的均匀性;另一个是所用的信号源本身在产生延时的过程中存在固有偏差。

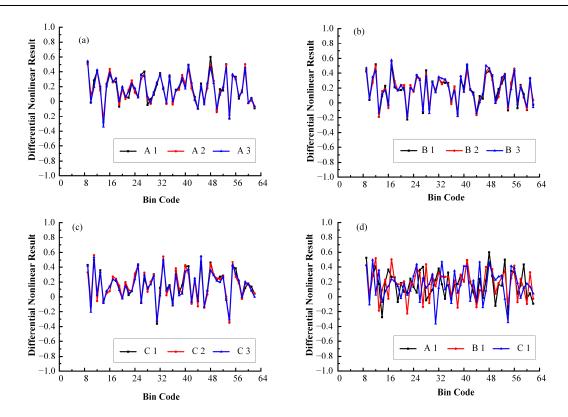

为排除信号源本身偏差带来的影响,设计如下 三组对照实验。各组实验中信号源设置的时间起点 和延迟时间均不相同,如果各组测试结果差异不大, 则可以说明微分非线性不是在信号源提供信号的过程中产生的,而是来自芯片本身的固有寄生参数。

保持温度、湿度、电压等其他实验条件不变,使用相同的信号源产生两路输出信号 OUT1 和OUT2。OUT1 输出后通过延迟盒再输入 TDC 作为START 信号,三组对照实验中,延迟盒的延迟时间分别设为 3.6 ns、5.6 ns、7.6 ns。OUT2 直接输入 TDC作为 STOP信号,通过上位机设置信号源 OUT2 的延迟时间分别从 3.6 ns、5.6 ns、7.6 ns 开始,每次步进 1 ps 直至其延迟时间增加到比起始值大 3.2 ns,同样对每个设置的延迟时间进行 500 次测试。

为增加论证的科学性,选用同一批设计的 3 个芯片进行以上对照试验,将 3 个芯片区分为 A、B、C。完成各组对照试验,得到 TDC 各延迟单元上的计数,计算出微分非线性,结果如图 6 所示。

图 6 对照实验微分非线性结果 (a) 芯片 A, (b) 芯片 B, (c) 芯片 C, (d) 芯片 A、B、C 在相同条件下 **Fig.6** Differential nonlinear results of comparative test (a) Chip A, (b) Chip B, (c) Chip C, (d) Chip A, B and C under the same condition

其中图 6(a)、(b)、(c)分别是芯片 A、B、C 各自对照实验的结果,图 6(d)是 3 个芯片在相同条件下的一组实验结果对比。由实验结果可以直观地看到图 6(a)、(b)、(c)中各组结果近似一致,而图 6(d)中3个芯片在相同条件下各 Bin 不均匀性存在差异,说明信号源本身对各 Bin 计数不均匀的影响很小,延迟链均匀性的缺失主要是芯片刻蚀加工过程中出现的寄生参数造成的。

由于芯片刻蚀加工过程中的误差是不能避免且 无法预估的,所以延迟链中最小延迟单元的时长也 难以精确控制,但是根据 ASIC 的特点,在环境相 对稳定的情况下,其寄生参数在芯片加工完成之后 就不会发生较大的变化。因此在使用之前可以对所 有延迟单元进行计算。

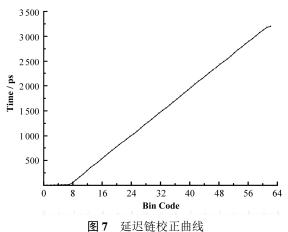

本文采用 Bin-by-Bin 方式对延迟链进行校准。利用 ADC 测试中标准的码密度测试方法可以对每个延迟单元大小进行测试<sup>[8]</sup>。产生 1200 000 个在测量动态范围内平均分布的随机信号给 TDC,并把读出的数据做直方图统计,直方图每个 Bin 中统计的数目正比于 TDC 实际的 Bin 延迟宽度,进而得出延迟单元的延迟宽度。

将所有TDC延迟单元Bin的延迟大小测量出来后存储为一个数组 $a_k$ 。则第n个延迟单元所对应的

时间  $t_n$  可表达为式(2)<sup>[9]</sup>,校准结果如图 7 所示,TDC 平均分辨率每 Bin 为 57 ps,与设计时的仿真结果相 吻合。

$$t_n = \frac{a_n}{2} + \sum_{k=0}^{n-1} a_k \tag{2}$$

Fig.7 Calibration curve of delay chain.

## 4 性能检测

根据测试得到的各延迟单元的大小将 TDC 刻度进行标定之后,对 TDC 的精度进行检测,给 TDC 的 START 和 STOP 两个输入端输入大量延迟时间固

040401-4

定的触发信号,将测得的数据进行统计分析,可以得到时间测量的均方根值(Root Mean Square, RMS)。在测试系统中,通过上位机设置信号源使两路输出信号间的延迟时间从 100 ps 开始,每组递增 100 ps,直到 3 000 ps。进行多组测试,每组重复测量 10 000 次,计算出各个延迟时间下 TDC 的 RMS值。测试结果表明: TDC 的 RMS值整体小于 40 ps,TDC 精度达到了预期的设计目标,也证明了本文所采用对照实验及刻度标定方法的可行性。

### 5 结语

本文基于 0.13 μm CMOS 工艺设计了一种可应 用在时间内插法中作为细计数模块的 TDC 芯片,实 现了一个能自动调节参数进行多次测量的闭环测试 系统。通过大量的测试和数据分析以及设计对照实 验进行验证,找到了 ASIC 设计中常见问题的可能 原因并给出了可行的修正办法,为后续完整 TDC 设计和测试问题的解决提供了一种可行的参考方 案。最终经实验验证,TDC 的分辨率达到每 Bin 57 ps,时间测试精度好于 40 ps,达到了预期的设计 目标。

# 参考文献

- 1 祁迹, 邓智, 刘以农. 一种基于 FPGA 的高精度单周期 TDC 设计[J]. 核电子学与探测技术, 2011, **31**(4): 378-385.

- QI Ji, DENG Zhi, LIU Yinong. A high accuracy single cycle TDC design based on FPGA[J]. Nuclear Electronics and Detection Technology, 2011, **31**(4): 378–385.

- 2 段霖. 多通道高精度时间数字变换器的电路实现[D]. 长沙: 湖南大学, 2013.

- DUAN Lin. Realization of multi-channel high precision digital-to-digital converter[D]. Changsha: Hunan University, 2013.

- 3 王巍, 董永孟, 李捷, 等. 基于 FPGA 的高精度多通道时间数字转换器设计[J]. 微电子学, 2015, **45**(6): 698-705.

- WANG Wei, DONG Yongmeng, LI Jie, et al. Design of

- high precision multi-channel time-to-digital converter based on FPGA[J]. Microelectronics, 2015, **45**(6): 698–705.

- 4 宋健. 基于 FPGA 的精密时间-数字转换电路研究[D]. 合肥: 中国科学技术大学, 2006.

- SONG Jian. Research on precision time-digital conversion circuit based on FPGA[D]. Hefei: University of Science and Technology of China, 2006.

- 李宏彬, 赫光中, 果秋婷. 基于皮尔逊相关系数的有机 质谱相似性检索方法[J]. 化学分析计量, 2015, 24(3): 33-37

- LI Hongbin, HE Guangzhong, GUO Qiuting. Methods for similarity retrieval of organic mass spectrometry based on pearson correlation coefficients[J]. Chinese Journal of Analytical Chemistry, 2015, **24**(3): 33–37.

- 6 吴军,王海伟,郭颖. 资源有限 FPGA 的多通道时间-数字转换系统[J]. 红外与激光工程,2015,44(4):1208-1217.

- WU Jun, WANG Haiwei, GUO Ying. Multi-channel time-to-digital conversion system with limited resources of FPGA[J]. Infrared and Laser Engineering, 2015, **44**(4): 1208–1217.

- Wu J Y, Shi Z H, Wang Y N. Firmware-only implementation of time-to-digital converter (TDC) in field programmable gate array (FPGA)[C]. Proceedings of the Nuclear Science Symposium Conference Record, IEEE, 2003.

- 8 刘树彬, 郭建华, 张艳丽, 等. 高精度数据驱动型 TDC 在高能物理实验中应用的研究[J]. 核技术, 2006, 29(1): 72-76.

- LIU Shubin, GUO Jianhua, ZHANG Yanli, *et al.* Study on the application of high precision data-driven TDC in high energy physics experiment[J]. Nuclear Techniques, 2006, **29**(1): 72–76.

- Wu J Y. Several key issues on implementing delay line based TDCs using FPGAs[J]. IEEE Transactions on Nuclear Science, 2010, 57(3): 1543–1548. DOI: 10.1109/ TNS.2010.2045901.