LI Xufeng, ZHOU Li, ZHU Yan, ZHAO Wenjie, HAO Cheng. System Design of a Common Circuit Board of Ground Test Instrument for Payload Data Handling System (in Chinese). Chinese Journal of Space Science, 2023, 43(5): 938–949. DOI:10.11728/cjss2023.05.2023–0009

# 载荷管理器通用地检测试板卡的系统设计\*

李旭峰  $^{1,2}$  周 莉  $^1$  朱 岩  $^1$  赵文杰  $^1$  郝 澄  $^1$

1(中国科学院国家空间科学中心 北京 100190) 2(中国科学院大学 北京 101499)

摘 要 地面检测设备用于对载荷管理器的功能和性能进行检测,是载荷管理器研发中的重要保障设备。由于不同型号任务中载荷硬件接口和软件协议差异较大,载荷管理器地检的通用性一直是地检设备的设计难点。提出了一种面向星上设备,尤其是载荷管理器的基于配置文件的通用地面检测设备测试板卡设计。针对不同任务中载荷管理器电接口的物理层约定、通信机制和遥测遥控不同的难题,采用软件配置和硬件可重构的方法实现板卡硬件的通用设计。针对不同任务的科学数据和总线协议数据格式不同的难题,采用基于序列解析的数据包生成方法和超时接收方法实现软件协议、数据格式可配置。通过测试验证了所提出的通用地检测试板卡设计的可行性和通用性。

关键词 地检,载荷管理器,可配置,可重构中图分类号 V19

# System Design of a Common Circuit Board of Ground Test Instrument for Payload Data Handling System

$\operatorname{LI} \operatorname{Xufeng}^{1,2} \quad \operatorname{ZHOU} \operatorname{Li}^1 \quad \operatorname{ZHU} \operatorname{Yan}^1 \quad \operatorname{ZHAO} \operatorname{Wenjie}^1 \quad \operatorname{HAO} \operatorname{Cheng}^1$

1(National Space Science Center, Chinese Academy of Sciences, Beijing 100190)

$2 ({\it University~of~Chinese~Academy~of~Sciences,~Beijing~101499})$

Abstract Ground Test Instrument (hereinafter referred to as GTI) tests the function and performance of a payload data handling system, and is an important support equipment in the design of a satellite's payload data handling system (hereinafter referred to as PHDS). Due to the great differences in the payloads' hardware interfaces and software protocols among different satellites, versatility has always been a problem for the design of a ground test instrument for PHDS. A common GTI circuit board design based on configuration files is proposed for on-board products, especially PHDS. To solve the problem of the difference in physical layer interfaces, communication mechanisms among different PHDS'

E-mail: lixufeng21@mails.ucas.ac.cn

<sup>\*</sup> 中国科学院国家重大科技专项项目资助(E16505B31S) 2023-01-17 收到原稿, 2023-04-23 收到修定稿

s electrical interfaces of different tasks, methods of software configuration and hardware reconfiguration are adopted in the hardware design of common test board. In view of the difference in the formats of scientific data and data bus protocol in different tasks, the GTI's software protocol and data format can be configurable by using the packet generation method based on sequence parsing and timeout reception method. Finally, the feasibility and versatility of the design of the common test board proposed in this paper are verified through the test.

Key words Ground test instrument, Payload data handling system, Common design, Reconfigurable

## 0 引言

在进行星上设备研发的同时,还需要设计有相应的地面检测设备(简称地检)对其进行功能和性能检测,确保满足任务要求<sup>[1]</sup>。卫星载荷分系统的载荷管理器负责星上有效载荷的统一供配电管理、遥测遥控、运行控制和数据处理,以及卫星平台与载荷之间的通信,是卫星重要功能部件之一。不同的卫星载荷分系统配置载荷的数量、硬件接口、软件协议等各不相同,导致不同型号任务的载荷管理器功能和接口各不相同,相应的载荷管理器地检需要进行个性化设计。不同型号任务载荷管理器的差异性使得地检的通用性一直成为设计难点<sup>[2]</sup>。

卫星平台对外电接口包括供配电接口、总线接口、科学数据输入接口、直接遥测输入接口、遥控输出接口、秒脉冲输出接口等<sup>[1-4]</sup>。载荷对外电接口包括供配电接口、总线接口、科学数据输出接口、直接遥测输出接口、遥控输入接口、秒脉冲输入接口等<sup>[5,6]</sup>。载荷管理器既连接卫星平台又连接多台载荷,因此载荷管理器接口分为对平台和对载荷两种。按照电接口传输速率可以分为高速接口和低速接口<sup>[6-8]</sup>;高速接口速率为几百 Mbit·s<sup>-1</sup> 至几 Gbit·s<sup>-1</sup>,通常采用同轴电缆或者光纤接口;低速接口包括速率小于100 Mbit·s<sup>-1</sup> 的接口,以及一些分立的遥测遥控接口。星上总线接口有1553 B总线、CAN总线、RS422总线、RS485总线等,星上低速科学数据接口包括单线制或者三线制的LVDS接口或者RS422接口。

载荷管理器地检的常规方案是每种接口使用独立的设备或硬件板卡实现,再通过一个或多个上位机控制。当前常规方案一般是采购工控机<sup>[3,9]</sup>,即带有PCIE接口的 1553 B 板卡、RS422 板卡、LVDS 板卡、模拟量采集板卡、OC 板卡等货架设备,每个板卡上有可编程器件 FPGA,在工控机进行上位机的界面

设计以及与每个板卡 FPGA 的接口和逻辑设计。这种方案的缺点是成本高,集成度低,软件设计复杂,需要编程的 FPGA 数量多,通用性差。为减少对地检的人力、物力和时间投入,提出一款硬件接口兼容性高、软件可配置、通用性高、使用成本低、与上位机接口简单的地检板卡,为多种任务型号的载荷管理器提供支持,加速管理器的研制进度,使得每个任务型号无需单独研制一台专用的地检。

本文根据地检实现通用性在数据格式与物理层约定的难点,针对以上问题,分析了板卡硬件设计和FPGA软件设计方法,并对地检测试板卡通用性进行测试,验证板卡设计的可行性。

# 1 地检测试板卡系统设计

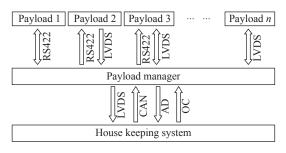

载荷分系统结构如图 1 所示。为了适配不同型号任务载荷分系统的硬件和软件接口协议<sup>[3,10-12]</sup>,基于配置文件的通用地检测试板卡的系统设计基本思想是: 地检测试板卡集成尽可能多通道的常用硬件接口, 在硬件上通过拨码开关或跳线实现物理层的兼容; 软件方面, 在 FPGA 设计时允许上位机通过配置文件修改内部寄存器, 并将配置文件存储在非易失性存储器 Nor flash 上, 后续上电自动从 Nor flash 加载

图 1 载荷分系统结构

Fig. 1 Load subsystem structure

寄存器配置,不需要重新配。适配不同任务时,FP-GA 代码不需要重新写,只需要设置对应的配置文件,达到通用的要求。

下面从硬件设计、FPGA设计和上位机设计三方面进行分析。

#### 1.1 硬件接口设计

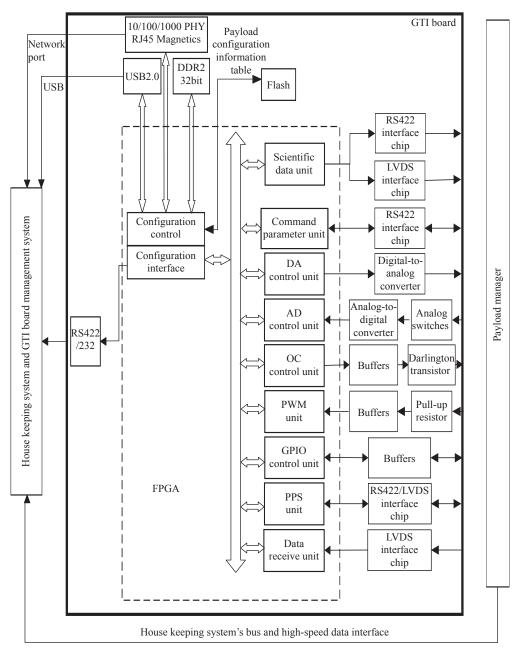

地检测试板卡系统架构如图 2 所示, 板卡由 4 部分组成, 包括与上位机的通信模块、缓存和配置文件模块、模拟平台接口模块和模拟载荷接口模块。

与上位机的通信模块包括 RS422 接口和百兆/千兆网口,用于接收上位机的指令和配置文件等,并且发送地检板卡状态和接收数据。缓存和配置文件模块由 SRAM 和 Nor flash 组成, SRAM 用于缓存科学数据, Nor flash 用于存储对应型号任务软硬件接口协议的配置参数。模拟的平台接口模块具备 OC 指令输出、遥测采集、秒脉冲产生、科学数据接收功能;模拟的载荷接口模块具备载荷总线响应、科学数据发送、载荷模拟量产生、OC 指令接收检测、秒脉冲接

图 2 地检测试板卡系统

Fig. 2 Block diagram of ground testing board system

收、GPIO 接口功能。

板卡硬件设计的硬件接口和通道数如表 1 所示, 能够满足绝大部分卫星平台、载荷硬件接口和数量的 要求;由于 1553 B 总线、CAN 总线板卡技术成熟,接 口标准,以及高速 Serdes 接口速率较高,因此未在地 检板卡中集成,可以采购货架板卡集成在工控机中。

板卡支持的科学数据和载荷总线通道,支持 UART协议、三线制 LVDS协议和单线制 8 B/ 10 B编码的 LVDS 协议。UART 协议的奇偶校验位、停止位、数据位和波特率可配置,数据位支持8位和7位,停止位支持1位、1.5位和2位。三线制LVDS 协议的使能和速率均可配置,支持低有效和高有效的使能,数据支持在时钟的下降沿或上升沿改变;单线制LVDS的 K码和速率均可配置。

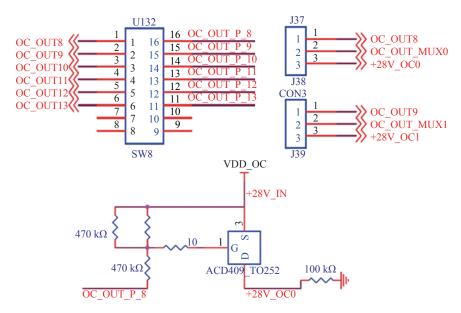

硬件的可重构设计基于拨码开关/跳线和通过软件重配置 FPGA 管脚控制寄存器实现。如图 3 所示,

表 1 通用地检测试板卡硬件接口

Table 1 Hardware interface of ground testing board

| 类别     | 功能       | 数量   | 可配置设计                                                              |

|--------|----------|------|--------------------------------------------------------------------|

| 模拟平台接口 | OC指令控制   | 14路  | 14路OC, 其中6路可配置成正电压模式                                               |

|        | 遥测采集     | 32路  | 每路AD为16位精度                                                         |

|        | 秒脉冲产生    | 2路   | 每路 PPS 输出可以精确控制 PPS 信号的占空比和单次脉冲的时间,<br>误差不超过 50 ns                 |

|        | 科学数据接收   | 16路  | 硬件上 16 路 LVDS 和 16 路 RS422, 每路科学数据可配成 RS422、三<br>线制 LVDS 和单线制 LVDS |

| 模拟载荷接口 | 载荷总线响应   | 20路  | 每路命令工参支持全双工和半双工的 RS422, RS422 的可配置项与科学数据接收相同                       |

|        | 科学数据发送   | 20路  | 20路RS422和20路LVDS, 硬件、软件配置与科学数据接收相同                                 |

|        | 载荷模拟量产生  | 256路 | 可输出0~5 V的电压                                                        |

|        | OC指令接收检测 | 96路  | 可以精确测量 OC 输入信号有效电平的时间和次数,误差不超过 100 ns,且支持高电平有效和低电平有效               |

|        | 秒脉冲接收    | 2路   | 接收检测秒脉冲                                                            |

|        | GPIO接口   | 32路  | 32路GPI和GPO                                                         |

|        | PWM输出    | 16路  | 可以精确控制脉冲周期、脉冲宽度和脉冲前沿,误差不超过50 ns                                    |

图 3 基于拨码开关/跳线的硬件可重构设计

Fig. 3 Hardware reconfigurable design based on dial switch/jumper

OC 指令输出通过拨码开关和跳线选择,若 OC 指令为输出低电平脉冲,拨码开关 U132 将置于关闭,跳线 J37 短接 1/2 两点;若输出指令为高电平脉冲,拨码开关 U132 将置于打开,驱动后级 MOSFET (U136)工作输出高电平,跳线 J37 短接 2/3 两点。

科学数据输入与输出选择 RS422 还是 LVDS 接口,由 FPGA 内部寄存器控制,该寄存器控制输入与输出接口连接内部 UART 逻辑、三线制或者单线制逻辑模块。具体通过一个寄存器控制多路器,根据寄存器的值导通多路器的相应通路实现。寄存器配置为 0 时,输入与输出使用 UART 协议;配置为 1 时,输入与输出使用三线制 PCM 协议;配置为 2 时,输入与输出使用 8 B/10 B单通道协议。

#### 1.2 FPGA 程序设计

FPGA 设计根据外部输出接口(见图 2),分为配置控制、科学数据、命令工参、DA 控制、AD 采集等功能模块,这里重点介绍配置控制、科学数据、命令工参等核心功能模块。

#### 1.2.1 配置控制模块

FPGA 通用性的设计由配置控制模块和 Nor Flash 实现。具体型号任务应用时需根据平台和载荷的接口类型、数量、数据格式对地检测试板卡上的 FPGA 寄存器进行配置,并将这些信息按照设计的地址定义存放到 Nor Flash 中;后续上电不需要上位机重新配置 FPGA 内的寄存器,由配置控制模块自动从

载荷配置的 Nor Flash 中将配置信息读到各功能模块。配置信息包括科学数据格式、载荷指令格式、工程应答格式、通信协议选择及配置、常用功能接口模块的配置。

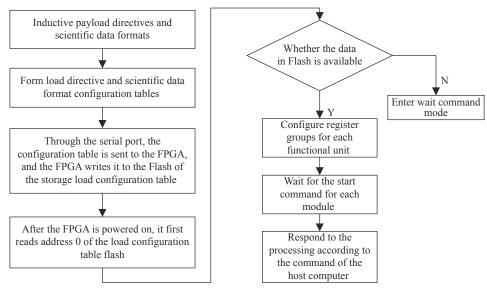

载荷管理器地检测试板卡的具体软件工作流程如图 4 所示。针对具体型号任务的载荷指令和科学数据格式,形成载荷指令和科学格式配置表;上位机通过串口将载荷指令和科学格式配置表发送给 FP-GA,由 FPGA 写入载荷配置表 Flash中。后续 FP-GA上电后,首先检查载荷配置 Flash 的地址 0,验证配置 Flash中的数据是否可用:如果可用,则按照载荷配置 Flash中数据配置各功能单元的寄存器组,等待上位机的启动命令,根据上位机的命令响应处理结果;如果不可用,则进入等待配置命令模式。

#### 1.2.2 科学数据模块

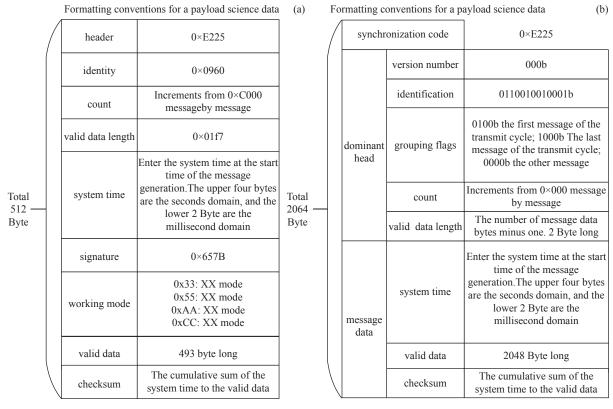

不同的任务型号科学数据以及指令应答数据包格式一般是不同的<sup>[6]</sup>,主要体现在数据包内字段的组成不同、单一字段长度不同、单一字段取值不同和数据包长度不同,如图 5 所示。科学数据与命令工参中多变的数据格式使得地检测试板卡 FPGA 设计很难通用。

针对这一难点,采用基于序列解析的数据包生成方法。将数据格式中的字段根据其特点进行分类、编码(见表 2)。科学数据与命令工参的数据包中固定不变的字段,例如包同步码、版本号、包标识、载荷标识

图 4 FPGA 配置控制模块工作流程

Fig. 4 FPGA configuration control module workflow

图 5 某两个任务型号科学数据的数据格式对比

Fig. 5 Data format comparison of scientific data of two task models

表 2 字段的抽象表示 Table 2 Abstract representation of fields

| 编码字段  | 编码  | 原始字段                 |

|-------|-----|----------------------|

| 固定字节  | 0x0 | 包同步码                 |

|       |     | 版本号                  |

|       |     | 包标识                  |

|       |     | 载荷标识                 |

| 校验字节  | 0x1 | CRC<br>校验和           |

| 填充字节  | 0x2 | 有效数据<br>科学数据         |

| 时间码字节 | 0x3 | 时间码                  |

| 计数字节  | 0x4 | 包序列计数<br>分组标识<br>包计数 |

等,定义为固定字节;循环冗余校验(CRC)、校验和等需要根据校验规则计算得出的字段,定义为校验字节;有效数据、科学数据等需要填入随机数或有序自增数的字段,定义为填充字节;需要填入实时时间的

时间码字段,定义为时间码字节;包序列计数、分组标识、包计数等起到计数作用的字段,定义为计数字节;在命令工参中,由于无需关注时间码、包计数等字段,因此均被归纳为无关字节。

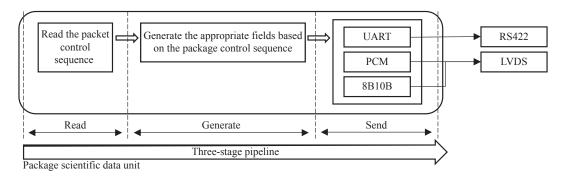

依照上述规则将具体数据包内各个字段转换为由编码表示的组包控制序列(见表 3),上位机将序列以及对应数据写入科学数据模块,科学数据模块根据读出的编码在数据包对应字节位置填入相应的数据。具体 FPGA 的实现如图 6 所示,分为读取、生成、发送三个阶段。读取是读取上位机发送过来的组包控制序列,生成是根据组包控制序列的编码填充数据包,发送是根据任务要求的协议产生相应的时序输出。

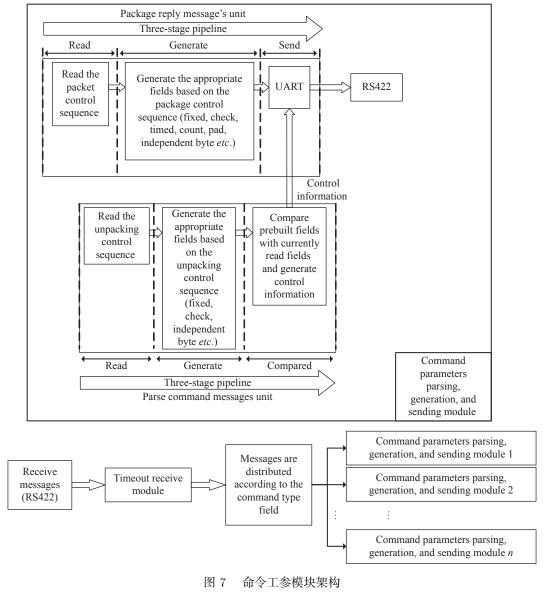

#### 1.2.3 命令工参模块

命令工参模块采用与科学数据模块相同的方法解决数据格式不同的问题,但命令工参模块还需要判断接收指令的有效性。具体实现方法是,命令工参模块会根据编码序列预生成一个字节,当收到一个字节时,会将当前接收到的字节与预生成的字节比较,然后根据编码序列生成下一个字节,以此循环。若两个字节不相同,则会生成错误信息发送至应答控制模

块,用于控制应答数据包的生成。

与科学数据包不同的是,在某些任务中,指令数据包的长度也存在较大差异,例如校时时间码指令只有6字节,而平台状态信息指令长数百字节。有的任务指令数据包存在有效数据字节数字段,有的任务指令数据包不存在有效数据字节数字段,无法推出整包的长度。因此在指令数据包不可预知长度时,判别指令数据包是否接收完毕,是地检测试板卡通用设计的另一个难点。

为此,采用一种超时接收的方法,即将依据长度 接收指令数据包转换为依据时间接收指令数据包。

表 3 科学数据报文实例

Table 3 Example of scientific data message

| 字节内容     | 取值            | 编码  |

|----------|---------------|-----|

| 包头标识     | 0xEB          | 0x0 |

|          | 0x90          | 0x0 |

| 载荷标识     | 0x44          | 0x0 |

| 包计数      | 从0x4000开始计数至  | 0x2 |

|          | 0x7FFF        | 0x2 |

| 可效数据字节数  | 有效数据字节数减1     | 0x0 |

| 时间码      | 高4字节填入秒域低2字节填 | 0x3 |

|          | 人毫秒域          | 0x3 |

|          |               | 0x3 |

| 有效数据1    | 随机数随机数随机数随机数  | 0x2 |

| 有效数据2    |               | 0x2 |

| 有效数据3    |               | 0x2 |

| 有效数据4    |               | 0x2 |

| 厚加和(高字节) |               | 0x1 |

| 累加和(低字节) |               | 0x1 |

当数据接收接口超过规定时间未接收到数据时,即认为指令数据包接收完毕。在任务型号中一般严格规定接收到指令数据包后的应答时间,为此设计了一个经验公式用于计算超时时间,保证命令工参模块可以接收到完整的指令数据包,并且应答数据包的时间间隔满足任务要求。

超时接收用于解决命令工参中指令数据包长度不可知的问题,以等待时间为依据判别指令数据包是否接收完毕。设超时接收等待时间为 T,当一个字节接收完毕后,若在时间 T内未收到下一个字节,则认为当前指令数据包接收完毕,将接收的数据送至指令解析单元,并复位接收单元准备接收下一个指令数据包。指令解析单元接收到指令数据包后,核验数据包的格式和内容是否正确。若数据包的格式与文件要求的格式不符,则不响应该条命令,并通过串口向上位机发送链路异常信息。若数据包的格式与文件要求的格式相符,则根据数据包内容的正误分别应答指令正确应答数据包和指令错误应答数据包。

在命令工参中不同类型的应答数据包的回复时间的要求一般是不同的,设一路命令工参存在n种应答数据包,每种应答数据包的回复时间最大不超过 $t_{i,\max}$ ,在吞吐率为1的情况下每种应答数据包发送完毕所需时间为 $t_{io}$ 。等待时间T不应大于 $T_{\max}$ ,即

$$T_{\text{max}} = \min\{t_{i,\text{max}} - 1.1t_i\}, i \in \{1, 2, 3 \dots n\}.$$

(1)

当时间 T小于  $T_{\max}$  才能严格保证应答数据包能 在规定时间内发送完毕。设接收一个字节的数据需要时间  $t_r$ ,则 T 应满足

$$T = \min\left\{T_{\text{max}}, 3t_{\text{r}}\right\}. \tag{2}$$

命令工参模块按照上述功能划分为解包单元和组包单元,如图 7 所示。解包单元与科学数据模块类

图 6 科学数据模块架构

Fig. 6 Scientific data module architecture

似,根据上位机配置的序列进行比对,将比对结果发送给组包单元,并增加了超时接收检测功能;组包单元根据接收到的指令进行组包,组包格式也是按照配置序列格式进行响应。命令工参模块目前支持最常用的 UART 协议。

整个功能单元按流水线处理,保证命令工参模块的吞吐率为1,并且发送应答包时不会因为数据未准备好而中断。

命令工参模块的设计解决了数据格式多样和指令数据包数据无法预知长度的问题,是一种与具体数据格式和数据长度无关的实现方法,具有更高的通用性。

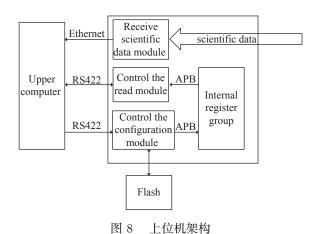

#### 1.3 上位机设计

上位机通过 RS422 接口对 FPGA 进行控制和状态读取,通过以太网口接收科学数据。如前所述,基于序列的配置文件由上位机生成。使用地检测试板卡时,只需要将给定需求/数据格式转化为对板卡寄存器的配置,再将全部寄存器待配置值组织成配置表写入 FPGA 内,即实现了 FPGA 参数的重配置。另外,上位机可以周期性读取各个功能接口采集到的数据并实时显示,为用户实时监测工程参数。

如图 8 所示, 板卡中设计了一片 Norflash 用于存储最新的寄存器配置表, 由上位机控制 FPGA 进行维护。板卡上电后, FPGA 自动读取存储在 Nor-

Structure of command working parameter module

Fig. 8 Upper computer architecture

Flash 内的寄存器配置表并配置内部寄存器,用户将 无需再次生成并写入寄存器配置表。寄存器配置表 可以通过上位机界面或者 excel 表生成,通过 excel 管 理寄存器配置表便于用户进行配置项编写、版本管理 和调试。

### 2 系统验证

以科学数据输出为例对板卡的通用性进行验证。科学数据输出功能是板卡的核心功能模块,也是板卡的设计要点。

#### 2.1 实验平台

搭建一套地检测试板卡测试平台,包含直流稳压电源、示波器、工控机箱、地检测试板卡和电压表各一块。另外,工控机箱配有一块PCIe接口的LVDS板卡,用于接收地检测试板卡发出的三线制LVDS和单线制LVDS数据,还配有一块MOXA盒通过RS422通路与板卡相连,用于向板卡发送命令工参的指令数据包并接收板卡的数据。示波器用于测量板卡接口的参数,电压表用于测量模拟量产生接口的模拟量,检查板卡的输出是否符合预期。

#### 2.2 科学数据模块通用性实验

为验证科学数据模块的通用性,首先设计了一系列接口测试例程,用于遍历接口的全部功能,其次选取多个任务型号的科学数据格式,测试科学数据模块产生的数据是否能满足全部要求。测试流程如下。

**步骤1** 根据表4通过上位机配置板卡,使板卡产生相应的接口。

**步骤 2** 使用示波器测试对应引脚,观察波形是

表 4 板卡传输接口测试例程

Table 4 Test routine of board transmission interface

| 接口                    |                                 | 测试                         | 项    |                |

|-----------------------|---------------------------------|----------------------------|------|----------------|

| UART<br>(RS422/RS485) | 波特率<br>/(bit·s <sup>-1</sup> )  | 奇偶校验位                      | 停止位  | 数据位宽<br>/(bit) |

|                       | 115200                          | 奇校验                        | 1位   | 8              |

|                       | 115200                          | 偶校验                        | 2位   | 7              |

|                       | 921600                          | 奇校验                        | 1.5位 | 8              |

|                       | 921600                          | 偶校验                        | 2位   | 8              |

|                       | 921600                          | 偶校验                        | 1位   | 8              |

| PCM<br>(三线制LVDS)      | 线速率<br>/(Mbit·s <sup>-1</sup> ) | 使能有效                       | 电平   | 边沿对齐方式         |

|                       | 1                               | 低电 <sup>工</sup>            | ŗ.   | 上升沿            |

|                       | 6                               | 高电互                        | F    | 上升沿            |

|                       | 12                              | 低电立                        | F    | 下降沿            |

|                       | 7                               | 高电互                        | ŗ.   | 下降沿            |

| 8B/10B<br>(单线制LVDS)   | 线道<br>/(Mb                      | 基率<br>it·s <sup>-1</sup> ) |      | 同步码            |

|                       | 1                               | 0                          |      | K28.5          |

|                       | 2                               | 0                          |      | K28.0          |

|                       |                                 | 1                          |      | K28.1          |

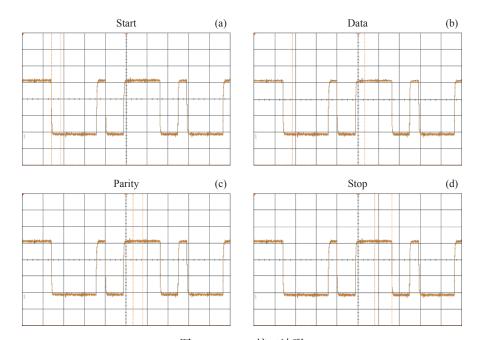

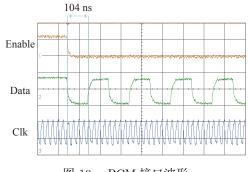

否符合预期。RS422接口需要关注波特率、校验位、起始位、停止位、数据位是否符合预期,如图 9所示。PCM接口需要关注线速率、使能有效电平和数据位变化时刻与时钟边沿的对齐情况是否符合预期,如图 10 所示。8B/10B需要关注线速率和同步码流是否符合预期,如图 11 所示。重复步骤 1 和步骤 2 遍历表 4 的测试用例。

步骤 3 以嫦娥系列任务型号的接口控制文件中 对科学数据的格式要求作为测试例程,通过上位机配 置板卡,使板卡发送对应数据。

步骤 4 使用 MOXA 盒和 LVDS 板卡接收数据,通过上位机观察接收的数据是否符合预期,如表 5 所示。其中 RS422 接口发送的数据通过 MOXA 盒接收, LVDS 接口发送的数据通过 LVDS 板卡接收。重复步骤 3 和步骤 4 遍历测试用例。

遍历表 4 和嫦娥系列任务型号的数据格式的全部测试用例后,测试结果全部符合预期。

#### 2.3 命令工参模块通用性实验

为验证命令工参模块的通用性,首先设计了一系列接口测试例程,用于遍历接口的全部功能,其次选取多个任务型号的命令工参数据格式,测试命令工参模块是否能正确解析指令数据包并应答对应的应答

图 9 RS422 接口波形

Fig. 9 Waveform of RS422 interface

图 10 PCM 接口波形

Fig. 10 Waveform of PCM interface

K28.5 Synchronous bitstreams

图 11 8B/10B 接口波形 Fig. 11 Waveform of 8B/10B interface

数据包。测试流程如下。

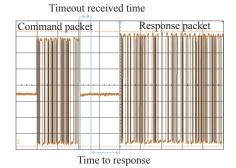

步骤 1 根据表 4 中 UART 部分通过上位机配置板卡,使板卡产生相应的接口。该模块还需要配置超时接收时间与应答间隔时间,如图 12 所示。

表 5 科学数据 Table 5 Scientific data

| 参数名称   | 接收值        | 实际值         |

|--------|------------|-------------|

| 包同步码   | E5         | E5          |

|        | 50         | 50          |

| 包标识    | 02         | 02          |

|        | 42         | 42          |

| 包序控制   | 80         | 自0x8000逐包自增 |

|        | 00         |             |

| 包数据域长度 | 00         | 00          |

|        | 07         | 07          |

| 时间码    | 00         | 2字节秒        |

|        | 01         |             |

|        | 00         | 2字节毫秒       |

|        | 00         |             |

|        | 00         | 2字节纳秒       |

|        | 07         |             |

| 有效数据   | 0A         | 0A          |

|        | BD         | BD          |

| 校验和    | 02         | 全部参数的累加和    |

|        | $_{ m CF}$ |             |

**步骤 2** 使用示波器测试对应引脚,观察波形是 否符合预期。

步骤 3 以嫦娥系列任务型号的接口控制文件中

图 12 命令数据包的接收与应答

Fig. 12 Command packet reception and response

# 表 6 指令正确应答数据包 Table 6 Response packet when command packet is correct

| 参数名称   | 接收值 | 实际值      |

|--------|-----|----------|

| 包头标识   | EA  | EA       |

|        | 50  | 50       |

| 载荷标识   | 07  | 07       |

| 应答码    | F0  | F0       |

|        | F0  | F0       |

| 包数据域长度 | 00  | 00       |

|        | 07  | 07       |

| 时间码    | 00  | 2字节秒     |

|        | 01  |          |

|        | 00  | 2字节毫秒    |

|        | 00  |          |

|        | 00  | 2字节纳秒    |

|        | 07  |          |

| 有效数据   | 1 A | 1 A      |

|        | 24  | 24       |

| 校验和    | 03  | 全部参数的累加和 |

|        | AC  |          |

对命令工参的格式要求作为测试例程,通过上位机配置板卡并发送指令数据包,使板卡应答对应的应答数据包。

**步骤 4** 使用 MOXA 盒接收数据,通过上位机观察接收的数据是否符合预期,如表 6 和表 7 所示。重复步骤 3 和步骤 4 遍历测试用例。

遍历表 4 和嫦娥系列任务型号的数据格式的全部测试用例后,测试结果全部符合预期。

#### 2.4 其他功能模块通用性实验

为了验证模块 OC 指令控制模块、模拟量生成模

表 7 指令错误应答数据包

Table 7 Response packet when command packet is wrong

| 参数名称 | 接收值 | 实际值                 |

|------|-----|---------------------|

| 包头标识 | EA  | EA                  |

|      | 50  | 50                  |

| 载荷标识 | 07  | 07                  |

| 应答码  | FF  | $\operatorname{FF}$ |

|      | FF  | FF                  |

表 8 板卡功能接口测试例程

Table 8 Test routine of board function interface

| 接口     | 测试项    |          |        |

|--------|--------|----------|--------|

| OC指令控制 | 有效电平   | 有效时间/ms  |        |

|        | 高电平有效  | 80       |        |

|        | 高电平有效  | 160      |        |

|        | 低电平有效  | 80       |        |

|        | 低电平有效  | 160      |        |

| 模拟量产生  |        | 电压/V     |        |

|        | 0.5    | 1.602    | 4.9218 |

|        | 1      | 1.836    | 3.3398 |

|        | 1.5    | 2.8125   | 1.3867 |

|        | 2      | 3.3007   | 0.3710 |

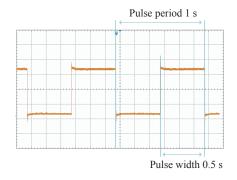

| PWM输出  | 脉冲周期/s | 脉        | 冲宽度/ms |

|        | 1(PPS) | 500(PPS) |        |

|        | 5      |          | 200    |

|        | 4      | 100      |        |

块、秒脉冲生成模块和 PWM 输出模块的通用性,设计了一系列接口测试例程,用于遍历接口的全部功能。

**步骤 1** 根据表 8 中接口测试例程配置板卡, 使板卡产生相应的接口。

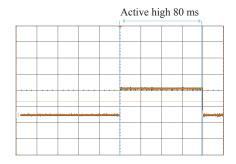

步骤 2 使用示波器和电压表测试对应引脚,观察波形是否符合预期。OC 指令控制模块需要关注有效电平与有效电平持续时间,如图 13 所示;模拟量生成模块需要使用电压表测量对应管脚,观察电压值是否与配置值相符,误差需要在±20 mV 内;秒脉冲生成模块与 PWM 输出模块基于同一模块实现,需要关注脉冲周期和脉冲宽度,如图 14 所示。

遍历表 8 的全部测试用例后,测试结果全部符合 预期。

图 13 OC 指令输出波形

Fig. 13 Waveform of Open Collector (OC)

图 14 PWM 输出波形 Fig. 14 Waveform of Pulse Width Modulation (PWM)

## 3 结论

针对不同型号任务载荷硬件接口和软件协议差 异大导致载荷管理器地检通用性差的难题,提出了一种硬件可重构、软件协议可配置的通用地检测试板卡的系统设计,该设计具有高集成度、高通用性、低成本、可重用、开发界面友好等优点,保证了项目研制进度,降低了对开发、成本和测试的需求。地检测试板卡已在嫦娥任务多台载荷管理器中得到应用,后续将支持空间科学卫星以及其他应用卫星等多个任务,具有较高应用价值。

#### 参考文献

- [1] ZHU Yan, BAI Yunfei, WANG Lianguo, et al. Integral technical scheme of payloads system for Chinese mars-1 exploration[J]. Journal of Deep Space Exploration, 2017, 4(6): 510-514,534 (朱岩, 白云飞, 王连国, 等. 中国首次火星探测工程有效载荷总体设计[J]. 深空探测学报, 2017, 4(6): 510-514,534)

- [2] ZHOU Changyi, WANG Chi, LI Huijun. Design of the payload subsystem of Chang'E-5 lunar explorer[J]. *Journ*-

- al of Deep Space Exploration, 2021, 8(3): 290-298 (周昌义, 王赤, 李慧军. "嫦娥五号" 探测器有效载荷分系统设计[J]. 深空探测学报, 2021, 8(3): 290-298)

- [3] WANG Lianguo, ZHU Yan, ZHOU Changyi, et al. Integrated payload OBDH technology for deep space exploration[J]. Journal of Space Science, 2018, 38(6): 960-970 (王连国, 朱岩, 周昌义, 等. 面向深空探测应用的集成一体化载荷数管技术[J]. 空间科学学报, 2018, 38(6): 960-970)

- [4] ZHANG H X, HE Q, LIU SH, et al. The design for LVDS high-speed data acquisition and transmission system based on FPGA[C]//2011 IEEE 3 rd International Conference on Communication Software and Networks. Xi'an: IEEE, 2011: 383-386

- [5] HARTONO R, ARDIANTO D, YATIM R, et al. Development of camera lens focus controller on LAPAN-A4 satellite payload[J]. AIP Conference Proceedings, 2021, 2366: 060001

- [6] RATIU O, PANAGIOTOPOULOS N, VOS S, et al. Wireless transmission of sensor data over UWB in spacecraft payload networks[C]//2018 6 th IEEE International Conference on Wireless for Space and Extreme Environments (WiSEE). Huntsville: IEEE, 2018: 131-136

- [7] WANG C L, LI Y, SHEN X H, et al. Design and implementation of spaceborne fast router based on SDRAM[C]//2019 IEEE 11 th International Conference on Communication Software and Networks (ICCSN). Chongqing: IEEE, 2019: 452-457

- [8] LIU Y F, ZHAO G Q, PENG X Y. Design and implementation of simulator for AOS high-speed payload multiplexer[C]//2013 IEEE 11 th International Conference on Electronic Measurement & Instruments. Harbin: IEEE, 2013: 285-290

- [9] MENG S W, PAN X F, YU J X, et al. A multi-channel multiplexer simulator for satellite on Zynq SoC[C]//2019 14 th IEEE International Conference on Electronic Measurement & Instruments (ICEMI). Changsha: IEEE, 2019: 1535-1541

- [10] LI Xiaobo, LI Wei, SUN Tianyu, et al. Analysis and design of onboard interface of Tianwen-1 high-resolution camera[J]. Optics and Precision Engineering, 2022, 30(2): 227-236 (李晓波, 李威, 孙天宇, 等. 天问一号高分相机星载接口分析与设计[J]. 光学 精密工程, 2022, 30(2): 227-236)

- [11] CAI Xiaowei, ZHI Jia, CHEN Zhimin, et al. Simulation method of spacecraft payload telemetry data based on correlation knowledge[J]. Computer Engineering and Design, 2022, 43(7): 2095-2101 (蔡晓玮, 智佳, 陈志敏, 等. 基于关联知识的航天器有效载荷遥测数据仿真方法[J]. 计算机工程与设计, 2022, 43(7): 2095-2101)

- [12] SEJERA M, YAMAUCHI T, ÖRGER N C, et al. Scalable and configurable electrical interface board for bus system development of different CubeSat platforms[J]. Applied Sciences, 2022, 12(18): 8964