新能源装备

HIGH POWER CONVERTER TECHNOLOGY

# 电动汽车驱动系统用控制板 EMC 仿真分析及优化

范祝霞, 罗家运, 支永健, 杨德勇 (南车电气技术与材料工程研究院, 湖南 株洲 412001)

摘要:以某电动汽车驱动系统控制板为对象,运用Ansys的仿真软件对其电磁兼容性进行建模、仿真,提出了改进设计的方法,并通过仿真进行了对比验证,证明了该方法的有效性。

关键词: 电动汽车; 电磁兼容; 电磁干扰; 串扰; EMI 仿真

中图分类号: TM153 文献标识码: A

文章编号: 2095-3631(2014)04-0036-04

doi:10.13889/j.issn.2095-3631.2014.04.009

## Simulation and Optimization of Control Board Used in Electric Vehicle Drive System

FAN Zhu-xia, LUO Jia-yun, ZHI Yong-jian, YANG De-yong

(CSR Research of Electrical Technology & Material Engineering, Zhuzhou, Hunan 412001, China)

**Abstract:** Based on a drive system control board of electric vehicle, modeling and simulation were performed for the EMC via Ansys simulation software, hence an improved design method was proposed. The effectiveness of this method was proved through simulation and comparison.

Keywords: electric vehicle; electromagnetic compatibility; electromagnetic interference; crosstalk; EMI simulation

### 0 引言

电子器件日益高频高速化的趋势以及应用环境的复杂性给电动汽车电子电路硬件设计带来许多新问题,其中电磁兼容性(EMC)问题尤为突出[1-2]。本文以某电动汽车驱动系统用控制板为研究对象,对该控制板的电磁兼容性进行了仿真分析并提出了优化方法。仿真结果表明,所提出的优化方法有助于提高整板的EMC性能。

### 1 电磁仿真模型的建立

本文仿真分析的驱动系统控制板主要由CAN总线通信电路、电机速度/位置处理电路、温度采集电路、电流电压信号采集电路、开关量输入输出电路、时钟电路

收稿日期: 2014-03-10

作者简介: 范祝霞(1982-), 女, 硕士, 工程师, 主要从事变流器 EMC 仿真工作。

以及各种保护电路等组成。

作为电机驱动系统的核心部件,控制板通过CAN网络与整车控制器交互指令和信息,结合控制板得到的逆变模块状态、电机速度/位置、电流、温度、母线电压信号等实现电机控制及相关保护功能,并将逆变器及电机相关信息通过CAN网络发送给整车控制器。

该驱动系统控制板采用晶振电路为控制芯片提供 其正常工作所需的频率为10 MHz、幅值为3.3 V的时钟 信号。由于晶振电路的精度和稳定性直接影响整个控 制电路的稳定性和可靠性,因此必须精确设计时钟信 号在PCB板上走线并分析晶振电路对其周围其他电路 产生的干扰。

该驱动系统控制板的PCB是采用Altium Designer Summer09绘制而成(图 $_1(_a)$ )。本文采用Ansys公司的PCB电磁仿真软件对该控制板进行电磁干扰(EMI)仿真分析。美中不足的是,该EMI仿真软件未能提供

Altium Designer Summer09接口支持。因各商用软件之间的接口并不匹配,且在数据格式和标准方面存在差异,导入过程可能导致部分数据缺失,所以应首先检查布线的连续性,将不完整的布线补全。之后可以得到用于Ansys下一系列PCB电磁仿真软件的初步模型(图1(b)),下文所述仿真均将以其为基础按需要进行建模。

(a) PCB图

(b) 仿真模型图

图1 控制板 PCB 图及仿真模型图

Fig. 1 PCB diagram of the control board and its simulation model

### 2 EMC 仿真分析及优化

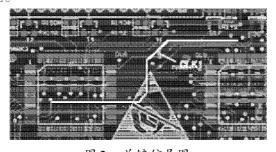

经验表明,PCB上90%的EMC问题是由10%的关键电路引起的,因此针对PCB的EMC仿真首先要识别出关键的干扰电路。根据分析可以知道,该控制板上晶振输出的时钟信号网络CLK1走线较长,且晶振电路时钟频率较高,最有可能对周围电路产生EMI,引发串扰问题。因此本文将重点关注晶振线对其邻近走线的串扰以及对空间的EMI辐射问题,并提出相应的优化措施以改进设计。图2中CLK1标识路径为所识别出的关键信号路径。

图 2 关键信号图 Fig. 2 The critical signal diagram

#### 2.1 串扰仿真及分析

串扰,从本质上讲,就是指相互靠近的导线和PCB

上所布的带状线之间无意的电磁耦合,实际上也就是一个近场耦合问题。在所有高速PCB电路的设计中,串扰现象非常普遍。串扰程度只能被降低但不可能完全避免。过大的串扰可能引起电路的误触发,导致系统无法正常工作。在PCB中,当有信号传递时,希望信号能从发送端在能量损失最小的情形下顺利地传送到接收端,而且接收端将其完全吸收而不产生任何信号反射[3-5]。

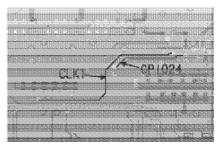

当网络CLK1不加地防护布线时,选取网络CLK1及其附近的信号线GPIO24进行串扰仿真分析。根据所选取的网络建立 S 参数模型并将之导入建立电路仿真模型。图3(a)为由最初设计图所转化得到的电磁仿真模型,其中选取了网络CLK1和其附近的信号线GPIO24,所选取的网络如图中CLK1和 GPIO24所示。当攻击线CLK1上传输信号的上升时间为0.1 ns、下降时间为0.1 ns、脉冲宽度为4 ns、周期为10 ns时,仿真得到的近端串扰和远端串扰如图3(b)所示。由此可以看出,串扰情况比较严重。

(a) 电磁仿真模型

(b)近端串扰和远端串扰信号波形图 图 3 仿真模型及结果

Fig. 3 The simulation model and results

在PCB设计中,对关键信号进行接地防护能有效降低电磁干扰。因此,晶振输出的时钟信号网络CLK1采取增加一个"地环"的设计,该"地环"将网络CLK1完全包住,并通过过孔连接至地,"地环"局部图如图4(a)中所示。图4(a)所示为晶振线增加"地环"之后所建立的电磁仿真模型,再次选取网络CLK1和其附近的信号线GPIO24进行串扰仿真分析,所选取的网络如图中CLK1和GPIO24所示。在攻击线CLK1为相同传输信号的条件下,得到的近端串扰和远端串扰如图4(b)所示。