# SCIENCE CHINA

# Information Sciences

• RESEARCH PAPER •

April 2013, Vol. 56 042402:1-042402:7 doi: 10.1007/s11432-013-4801-1

# 4-channel, 40 Gb/s front-end amplifier for parallel optical receiver in 0.18 $\mu m$ CMOS

CHEN YingMei\*, ZHU Lei, ZHANG Li & LI Wei

Institute of Radio Frequency- & Optoelectronic-Integrated Circuits, Southeast University, Nanjing 210096, China Received November 6, 2012; accepted December 14, 2012; published online February 5, 2013

Abstract This paper proposed a 4-channel parallel 40 Gb/s front-end amplifier (FEA) in optical receiver for parallel optical transmission system. A novel enhancement type regulated cascade (ETRGC) configuration with an active inductor is originated in this paper for the transimpedance amplifier to significantly increase the bandwidth. The technique of three-order interleaving active feedback expands the bandwidth of the gain stage of transimpedance amplifier and limiting amplifier. Experimental results show that the output swing is 210 mV (Vpp) when the input voltage varies from 5 mV to 500 mV. The power consumption of the 4-channel parallel 40 Gb/s front-end amplifier (FEA) is 370 mW with 1.8 V power supply and the chip area is 650  $\mu$ m × 1300  $\mu$ m.

**Keywords** enhancement type regulated cascade (ETRGC), active inductor, transimpedance amplifier, limiting amplifier, three-order interleaving active feedback

Citation Chen Y M, Zhu L, Zhang L, et al. 4-channel, 40 Gb/s front-end amplifier for parallel optical receiver in 0.18  $\mu$ m CMOS. Sci China Inf Sci, 2013, 56: 042402(7), doi: 10.1007/s11432-013-4801-1

# 1 Introduction

With characteristics such as large capacity and high speed data rate, optical fiber communication has developed rapidly in network and multimedia applications. Parallel transmission is an important method to increase the speed of optic-fiber communication integrated circuits, at the same time it has the advantage of simple structure and short latency time over serial interconnects. In synchronous communication system, optical signal has become very week in the receiving end after traveling dozens or even hundreds of kilometers. The front-end amplifier (FEA) aims to convert the week current pulse from PD to a certain limiting voltage signal and introduce noise as little as possible.

A low power FEA is designed in TSMC 0.18 µm CMOS technology in this paper, which consists of transimpedance amplifier (TIA) and limiting amplifier (LA). The FEA is the most critical element in an optical receiver affecting the whole system performance such as speed, sensitivity, and signal-to-noise ratio. Hence, the design mandates careful optimization of a number of tradeoffs among bandwidth, gain, and noise. For high speed application, some broadband techniques are employed in circuit design. In TIA, the input stage adopts a novel enhancement type regulated cascade (ETRGC) configuration with an active inductor to expand bandwidth, while the gain stage chooses three-order interleaving active feedback to acquire a high gain and broad bandwidth at the same time. In LA, three-order interleaving active feedback is also employed in the core units.

<sup>\*</sup>Corresponding author (email: njcym@seu.edu.cn)

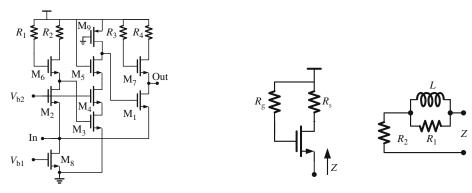

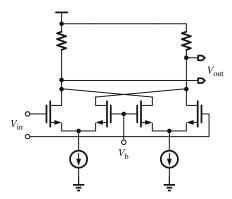

Figure 1 Circuit of input stage.

Figure 2 Circuit and equivalent model of active inductor.

# 2 TIA design

The front-end amplifier (FEA) consists of transimpedance amplifier (TIA) and limiting amplifier (LA). TIA is aimed to convert a week current from PD to voltage signal, and the voltage signal will be further amplified by the following LA. The TIA is constructed by the input stage and the gain stage.

### 2.1 Input stage

As the first stage of TIA as well as the front-end amplifier, the input stage has to convert current signal to voltage. To reduce the influence of parasitic capacity of PD effectively, it is demanded that the input impedance of TIA should be designed as small as possible.

As illustrated in Figure 1, the input stage employs the configuration of enhancement type regulated cascade (ETRGC), and it consists of three stages of voltage gain of  $A_1$ ,  $A_2$  and  $A_3$ . The  $A_1$ ,  $A_2$  and  $A_3$  is the voltage gain of input node to source of  $M_6$ , source of  $M_6$  to gate of  $M_1$ , and gate of  $M_1$  to output, respectively, which can reduce the input impedance effectively and ensure a sufficient gain and bandwidth. The transimpedance gain  $Z_{TIA}$  can be approximated as follows [1–3]:

$$Z_{\text{TIA}} = \frac{Z_{\text{out}}}{1 + sC_{\text{i,total}}Z_{\text{out}}/A_1A_2A_3},\tag{1}$$

where  $Z_{\text{out}}$  is the output impedance, and  $C_{\text{i,total}}$  is the total input capacity.

From the (1), it can be seen that the bandwidth can be expanded effectively by enlarging the voltage gain of  $A_1$ ,  $A_2$  and  $A_3$ . To further improve the bandwidth, a structure of active inductor as shown in Figure 2 is also employed. The equivalent model of active inductor is shown in Figure 2. Ignoring second effects, the equivalent output impedance and equivalent inductance can be expressed as follows[4]:

$$Z_{\text{out}} = \frac{1 + sR_{\text{g}}C_{\text{gs}}}{g_{\text{m}} + sC_{\text{gs}}},\tag{2}$$

$$L = \frac{C_{\rm gs}}{q_{\rm m}} \left( R_{\rm g} - 1/g_{\rm m} \right). \tag{3}$$

As shown in (2),  $|Z_{\text{out}}|$  increases with frequency and behaves as an inductor. According to the PVT analysis, the  $|Z_{\text{out}}|$  can retain inductive with the appropriate value of  $R_{\text{g}}$  and  $1/g_{\text{m}}$ . Thus, the bandwidth of input stage is further improved by this inductive load.

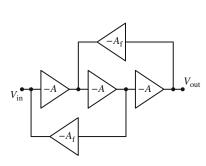

#### 2.2 Gain stage

As the second stage of TIA, the gain stage is proposed to further enlarge the signal generated by input stage. To ensure the demand of bandwidth, the three-order interleaving active feedback configuration is shown in Figure 3. Assume each node has a load of  $R_{\rm L}/(1/sC_{\rm L})$ , the transfer function is given by [5]:

$$\frac{V_{\text{out}}}{V_{\text{in}}}(s) = -\frac{A^{3}(s)}{1 + 2A^{2}(s)A_{f}(s)},$$

(4)

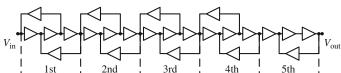

Figure 3 Architecture of three-order interleaving active feedback.

Figure 4 Circuit of three-order interleaving active feedback.

where  $A(s) = A/(1 + s/\omega_0)$ ,  $A_f(s) = A_f/(1 + s/\omega_0)$ ,  $\omega_0 = R_L C_L$ . A and  $A_f$  are the voltage gain of feed-forward and feedback path respectively.

By substituting A(s) and  $A_f(s)$  into transfer function, three poles are obtained as follows:

$$\omega_{p1} = -\omega_0 \left( 1 + \sqrt[3]{2A^2 A_{\rm f}} \right),\tag{5}$$

$$\omega_{p2,3} = -\omega_0 \left( 1 - \frac{1}{2} \sqrt[3]{2A^2 A_f} \pm j \frac{\sqrt{3}}{2} \sqrt[3]{2A^2 A_f} \right). \tag{6}$$

It is seen that by using three-order interleaving active feedback, the poles of the transfer function has been greatly postponed by  $A_{\rm f}$ , thus the bandwidth is enlarged.

Figure 4 shows the circuit of three-order interleaving active feedback. The  $M_1$ ,  $M_2$  and  $M_3$  are feed-forward common source amplifiers, and the  $M_4$  and  $M_5$  constitute feedback path.

To reduce the total integrated noise, the bandwidth of the TIA must be minimized, but the limited bandwidth introduces intersymbol interference (ISI) in random data. (7) denotes the relationship between the bandwidth and the produced across-zero jitter:

$$\frac{T_1 - T_2}{T_b} \approx \frac{R_b}{2\pi f_{-3dB}} \exp\left[\frac{-2\pi f_{-3dB}}{R_b}\right],\tag{7}$$

where  $T_{\rm b}$  represents the period of the data streams,  $T_1 - T_2$  is the across-zero jitter and  $R_{\rm b}$  denotes the bit rate of the data streams. If  $f_{-3{\rm dB}} = 0.5R_{\rm b}$ , then the jitter is 1.38%; and if  $f_{-3{\rm dB}} = 0.7R_{\rm b}$ , the jitter decreased to 0.28%. The trade-off between noise and ISI appears to improve as the bandwidth goes from  $0.5R_{\rm b}$  to  $0.7R_{\rm b}$  [6]. In this design,  $0.8R_{\rm b}$  is chosen because actual circuits may contain more poles, in addition technology and temperature variations mandate additional margin.

## 3 LA design

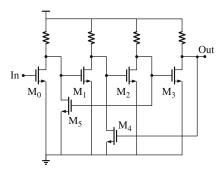

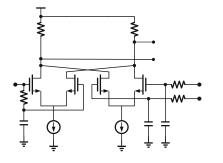

LA is proposed to amplify the voltage signal from TIA to a certain amplitude to meet the need of follow-up clock and data recovery circuit (CDR). LA is constructed by the input buffer, the five broadband-amplify core cells and the output buffer. Noting that the final output is a limiting signal, the last stage should be worked in large signal state.

As the input buffer of LA, it has to convert the single end signal from TIA to differential signal to meet the need of follow-up. At the same time, there exists DC offset in practical circuit for the reason of unmatched, which means the input buffer has a task of DC offset cancellation. The circuit of the input buffer is shown in Figure 5. High-frequency signal and the DC level extracted by RC low-pass filter are sent to a differential amplifier, which realizes single-to-differential conversion. On the other hand, the extracted DC component from the signal between five broadband-amplify cells and output buffer is sent to input buffer, thus achieves the function of DC offset cancellation.

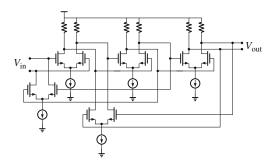

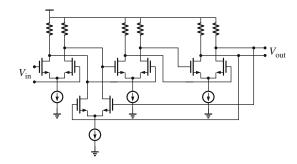

The architecture of the core circuit is shown in Figure 6, the core circuit of LA is composed of five broadband amplify cells. The front four cells employ three-order interleaving active feedback architecture,

Figure 5 Circuit of input buffer.

Figure 6 Architecture of core circuit of LA.

Figure 7 Circuit of the front four cells.

Figure 8 Circuit of the fifth cell.

Figure 9 Circuit of output buffer.

similar to the gain stage of TIA [7–9]. Noting that the signal in LA is differential, the amplify cells are realized in differential form correspondingly. The circuit of the front four cells and the fifth cell are shown in Figure 7 and Figure 8 respectively. To obtain a better large signal characteristic, the fifth cell employs traditional three-order active feedback, instead of the interleaving one.

An output buffer is usually required in LA as well as FEA. As shown in Figure 9, the output buffer adopts a structure of dual  $f_{\rm T}$ . This structure can put the input gate capacitances  $C_{\rm GS}$  of two input transistors in series to reduce the  $C_{\rm GS}$  into half [10], thus increasing the speed of output buffer drastically.

# 4 Simulation and experimental results

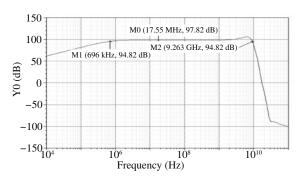

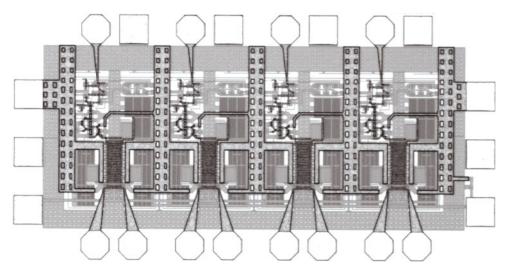

The 4-channel parallel 40 Gb/s front-end amplifier is designed in TSMC 0.18  $\mu$ m CMOS technology. The layout of each 10 Gb/s channel grid has a pitch of 250  $\mu$ m. To suppress the substrate and supply coupling noise from adjacent channels, each channel is surrounded by two P+ and N well guard rings. The P+ guard ring is connected to ground and the N well guard ring is connected to power supply, this reverse biased pn junction can suppress the substrate and supply coupling noise significantly. Assuming the parasitic capacitance of PD and the input bondiong PAD of the layout is 200 fF, the simulated frequency

**Figure 10** The simulated gain-bandwidth response of the FEA.

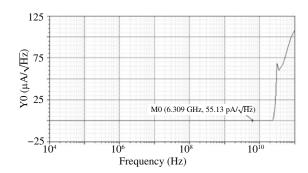

Figure 11 The equivalent input noise current of the FEA.

Figure 12 Micrograph of 4-channel parallel 40 Gb/s FEA.

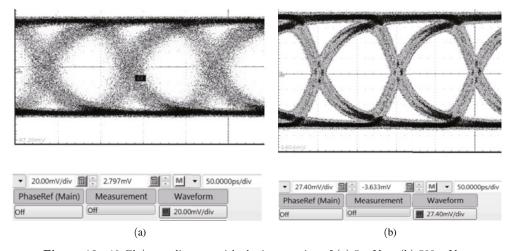

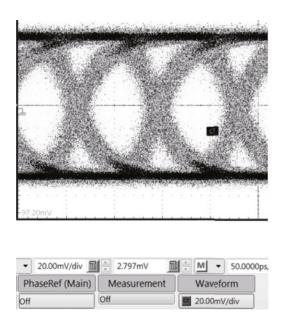

Figure 13  $\,$  10 Gb/s eye diagram with the input swing of (a) 5 mV  $_{pp};$  (b) 500 mV  $_{pp}.$

response of the TIA and LA is shown in Figure 10 and the -3 dB bandwidth is 9.26 GHz. The equivalent input noise current spectral density of the FEA is 55.13 pA/ $\sqrt{\rm Hz}$  as shown in Figure 11. The micrograph of the 40 Gb/s FEA chip is shown in Figure 12 and it occupies an area of  $650~\mu m \times 1300~\mu m$ .

The measured output eye diagrams of a single FEA channel with differential outputs at 10 Gb/s with 5 mV and 500 mV is shown in Figure 13(a) and Figure 13(b), respectively. Considering the input impedance is 50 ohm, so the FEA exhibits a sensitivity of 100  $\mu$ A input current. The maximum 12 Gb/s

Figure 14  $\,$  12 Gb/s eye diagram with the input swing of 20 mV<sub>pp</sub>.

Table 1 Performance comparison with other works

| Design                                  | Ref. [11]                 | Ref. [12]                 | This work                 |

|-----------------------------------------|---------------------------|---------------------------|---------------------------|

| Function                                | TIA+LA                    | TIA                       | TIA+LA                    |

| Technology                              | $0.18~\mu\mathrm{m~CMOS}$ | $0.18~\mu\mathrm{m~CMOS}$ | $0.18~\mu\mathrm{m~CMOS}$ |

| Maximum channel rate (Gb/s)             | 10                        | 40                        | 12                        |

| Bandwidth (GHz)                         | 7.6                       | 30.5                      | 9.3                       |

| $C_{pd}$ (fF)                           | 150                       | 50                        | 200                       |

| Sensitivity                             | $-12~\mathrm{dBm}$        | 135.8 μΑ                  | 100 μΑ                    |

| $\mathrm{Gain}\ (\mathrm{dB}\Omega)$    | 87                        | 51                        | 98                        |

| Output swing                            | 400                       |                           | $210~\mathrm{mV}$         |

| Inductor counts                         | 8                         | 15                        | 0                         |

| ${\rm Area}~({\rm mm}{\times}{\rm mm})$ | $1.028\times1.796$        | $1.17\times0.46$          | $0.65\times0.325$         |

| Power (mW)                              | 210                       | 60.1                      | 92 mW per channel         |

output eye diagram of the single FEA channel is shown in Figure 14. The output eye diagram maintains stable and clear with a limiting range of output voltage of 210 mV<sub>pp</sub> on 50  $\Omega$  load.

The circuit performance comparison of this 40 Gb/s front-end amplifier and prior works [11,12] is summarized in Table 1. The proposed inductorless FEA is power, cost, and area efficient for the 40 Gb/s parallel optical fiber communication systems.

#### 5 Conclusions

This paper proposed a single-chip optical receiver front-end amplifier array for 40 Gb/s parallel optical transmission systems in a standard TSMC 0.18 µm CMOS technology. A novel enhancement type regulated cascade (ETRGC) configuration with an active inductor has been contrived in this paper for the TIA to broaden the bandwidth. The technique of three-order interleaving active feedback expands the bandwidth of the gain stage of TIA and LA. The experimental results show that the entire front-end amplifier has a large dynamic range, low power consumption and low cost, which is suitable for high-speed parallel data transmission.

# Acknowledgements

This work is supported by National High-tech R&D Program of China (863 Program) (Grant No. 2011AA010301) and National Natural Science Foundation of China (Grant No. 60976029).

#### References

- 1 Kromer C, Sialm G, Morf T, et al. A low-power 20-GHz 52-dB transimpedance amplifier in 80 nm CMOS. IEEE J Solid-State Circuit, 2004, 39: 885–894

- 2 Chan C-T, Chen O T-C. A 10 Gb/s CMOS optical receive using modified regulated cascode scheme. In: Proceedings of the 48th IEEE Midwest Symposium on Circuits and Systems, Covington, 2005. 171–174

- 3 Park S M, Yoo Y-J. 1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications. IEEE J Solid-State Circuit, 2004, 39: 112–121

- 4 Sansen W M. Analog Design Essentials. Springer, 2006. 72-74

- 5 Huang H-Y, Chien J-C, Lu L H. A 10-Gb/s inductorless CMOS limiting amplifier with third-order interleaving active feedback. IEEE J Solid-State Circuit, 2007, 42: 1111–1120

- 6 Razavi B. Design of Integrated Circuits for Optical Communications. New York: McGraw-Hill, 2002

- 7 Zhu L, Chen Y M, Tian L, et al. A 10 Gb/s low-power front-end amplifier for optical receiver in 0.18 μm CMOS technology. In: Proceedings of the International Conference on Mechanical and Electronic Engineering, Weihai, 2012. 24–26

- 8 Chan C-T, Chen O T-C. Inductor-less 10 Gb/s CMOS transimpedance amplifier using source-follower regulated cascode and double three-order active feedback. In: Proceedings of IEEE International Symposium on Circuits and Systems, Island of Kos, 2006. 5487–5490

- 9 Chen Y M, Wang H, Yan S C, et al. A 10 GHz multiphase LC VCO with a ring capacitive coupling structure. Sci China Inf Sci, 2012, 55: 2656–2662

- 10 Xu Z G, Chen Y M, Wang T. A 40-Gb/s fully integrated CMOS optical receiver analog front-end in 90-nm CMOS. J China Univ Post Telecommun, 2012, 19: 124–128

- 11 Chen W Z, Cheng Y L, Lin D S. A 1.8-V 10-Gb/s fully integrated CMOS optical receiver analog front-end. IEEE J Solid-State Circuit, 2005, 40: 1388–1396

- 12 Jin J D, Hsu S S H. A 40-Gb/s transimpedance amplifier in 0.18- $\mu$ m CMOS technology. IEEE J Solid-State Circuit, 2008, 43: 1449–1457