# 亚纳秒触发脉冲延时分配器设计

狄兰兰 谷鸣 袁启兵 范学荣 (中国科学院上海应用物理研究所 上海 201800)

摘要 介绍了上海光源储存环注入系统冲击磁铁定时触发脉冲延时分配器的设计和研制。采用可控专用延时芯片设计了该触发脉冲延时分配器,实现 1 路光脉冲输入, 4 路延时独立可调的快前沿低抖动电脉冲输出,输出脉冲延时调整步长 0.25 ns、可调延时范围 64 ns。除具有延时功能外,还具有联锁保护、输出脉冲状态、联锁输入状态显示等功能,不仅可以通过仪器面板操作,还可以通过 RS232 接口遥控。

关键词 亚纳秒,延时分配器 中图分类号 TN786

上海同步辐射装置(SSRF)由直线加速器、增强 器、储存环组成,各部分设备的定时触发信号都由 主定时系统[1]提供。SSRF 储存环注入系统采用 4 块 冲击磁铁作为电子束闭环凸轨磁铁,而注入系统以 TOP-UP 模式将电子束注入到储存环,对凸轨冲击 磁铁的磁场匹配和稳定性能提出很高要求。其中, 凸轨冲击磁铁的磁场建立时间是影响磁场匹配性能 的重要因素。冲击磁铁制造与安装引入的误差,磁 场建立时间对触发脉冲的响应会有不同的延迟;同 时,电子束的飞行时间使4块冲击磁铁的磁场建立 时间(触发时间)不在同一时刻, 就须对 4 块冲击磁 铁的脉冲磁场建立时间做精确、细微的定时调整, 使电子束经过冲击磁铁时感应相同的磁场强度,使 储存环束流的闭轨参数不受影响,或受尽量小的影 响。则需将主定时系统提供的定时光脉冲转化为电 脉冲,并作精确延时后触发4块冲击磁铁磁场建立。

最简单可靠的电脉冲延时方法是同轴电缆模拟延时,此法成本低,但其延时值取决于电缆长度,长时间延时需长电缆。光脉冲可用光纤模拟延时<sup>[2]</sup>,其优缺点类似于同轴电缆。集成脉冲延时电路的优点,是延迟时间可实现数字化控制。集成有源延时的实现方案,可用高频率时钟脉冲计数的方法产生延时脉冲,也采用集成模拟延时芯片。前者原则上可实现无限长的延时,且延时准确度高,但是其最小延时步长取决于很高的时钟频率和高频电路,研制成本高、电路复杂,Stanford Research Systems 的数字延迟脉冲发生器 DG535 就采用这种设计方法,最小延时步长 5 ps,总延时 1000s<sup>[3]</sup>,但是价格很高;集成模拟延时芯片的最小延时步长固定,有 4-10

位的延迟时间控制数据端口,用于设置延迟时间, 延迟时间为延时步长的倍数。本文采用集成模拟延 时芯片,其电路简单,设计灵活,可根据所需延时 步长和范围选择延时芯片<sup>[4-6]</sup>。

# 1 硬件电路

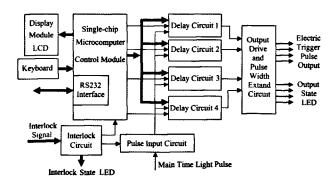

根据 SSRF 储存环物理要求,为方便操作和控制,设计了延时分配器硬件电路(图 1),其包括脉冲输入电路、4 路延时电路、联锁保护电路、单片机模块(带 RS232 接口)、输出驱动和脉冲展宽电路、键盘和 LCD 显示电路等。

图 1 延时分配器的功能方框图

Fig.1 Functional block diagram of delay and assignation apparatus.

SSRF 主定时系统的定时信号是光脉冲信号,而冲击磁铁所需触发信号是电脉冲,脉冲输入电路把从主定时系统光纤输入的光信号转换成电脉冲,经延时电路和驱动电路处理后输出,作为冲击磁铁系统的触发脉冲。为确保设备安全运行,延时分配器设有联锁保护电路,只有当输入的 4 路联锁信号都

第一作者: 狄兰兰, 女, 1982年3月出生, 2008年于中国科学院上海应用物理研究所获硕士学位

通讯作者:谷鸣

收稿日期: 2011-01-15, 修回日期: 2011-06-10

为允许时,脉冲输入电路工作,输出触发脉冲。从脉冲输入电路输出的电脉冲同时送给 4 路延时电路,每路对输入脉冲的延迟时间通过键盘或遥控输入,显示在 LCD 上。输入的延时数据经单片机C8051F340处理后设置每路延时芯片的延时。延时分配器以单片机模块作为内部控制部件,带有RS232接口[4,7],便于遥控设置和监测延时分配器每路输出的延迟时间和状态。

### 1.1 集成模拟延时芯片

完成延时功能的集成模拟延时芯片有很多种,它们的共同特点是:延时步长固定(如 10 ps 或 0.25、0.5、1、5、10 ns 等),有并行或串行延时设置数据端口,延时可调范围与步长和控制数据位的位数有关<sup>[8]</sup>。根据储存环物理设计和芯片功能分析和调研,本文选用 DS1023S-25 芯片(Dallas Semiconductor)。

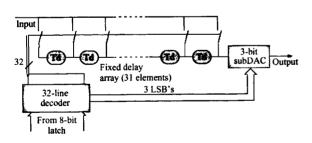

该芯片的延时调整步长是 0.25 ns, 8 位延时控制数据位,延时调整范围 64 ns<sup>[9]</sup>。对触发脉冲的延时功能由一系列延时单元和一个 SubDAC 完成,可控制功能由译码器和可控开关完成,延时原理如图 2。DS1023S-25 有 31 个延时单元和一个 3-bit 的SubDAC。每个延时单元对输入触发脉冲延时 2 ns; SubDAC 的最大延时是 2 ns,延时精度是 0.25 ns。工作时,延时控制位的高 5 位经译码器译码后,选择延时单元的串延时间,控制位的低 3 位控制SubDAC 的延时。

图 2 DS1023S-25 延时功能的实现原理 Fig.2 Principle of DS1023S-25 time delay function.

3-bit SubDAC 由 3-bit DAC、斜波发生器和比较器各一个组成。斜波发生器由经过延时单元的脉冲触发,DAC 的输出作为比较器的参考电压,斜波发生器的输出与参考电压比较,相等时,比较器的输出翻转,实现脉冲延时。

DS1023S-25 的延时设置模式为并行模式时,延时设置数据从 8 位数据端口并行输入 8 位寄存器;串行模式时,串行延时设置数据在时钟上升沿,以MSB 到 LSB 的顺序输入到 8 位寄存器,再由锁存允许信号将寄存器中数据送入 8 位锁存器。锁存允

许信号为低电平时,数据端口的最后状态被 8 位锁存器锁存,锁定触发脉冲信号的延迟时间。数据端口逻辑状态的改变不影响对触发脉冲的延时。

#### 1.2 控制模块

触发脉冲延时分配器的内置控制部件采用C8051F340单片机开发板,其有40个 I/O 口线,可同时使用硬件 SMBUS、SPI 和 UART 串口,片内调试电路提供全速、非侵入式的在系统调试(无需仿真器)<sup>[10]</sup>。该开发板带有 RS232 接口、USB 接口和在系统调试连接端口,编程调试以及与其它控制器通信方便。C8051F340 模块控制 4 路 DS1023S-25 延时电路的延时控制位设置及片选、延时状态的 LCD显示、键盘输入以及 RS232 通信接口,单片机的 I/O口与这些电路连接。

模块中的 RS232 接口可连接 DB9 接头的 2、3、7、8 和 5 脚,即 Rx、Tx、RTS、CTS 和 GND。由于单片机的输入输出电平是 TTL 电平,RS232 通信使用的是 +5 V~+15 V 和 -5 V~-15 V 的负逻辑电平,控制模块中在单片机的串行 I/O 口和 RS232 接口间用电平转换电路,将单片机的 TTL 电平转换成 RS232 电平。

# 1.3 键盘电路

延时分配器的面板操作键盘为 6 个机械触点开关,用作本地操作参数设置,分别与单片机的 6 个 I/O 口连接,键按下相应 I/O 口为低电平,弹起为高电平。单片机通过扫描 6 个 I/O 口的输入电平,确定是否有键按下,是哪个键按下,再执行相应的操作。6 个按键中,一个"设置"键,按一下 LCD 显示4 个通道的初始状态,不按该键,其它所有键无效,LCD 无显示;一个"通道"键,用于循环选择 4 路延时电路,选中通道的延时才可以调节,此时,按一下"增加"或"减小"键,该通道的延时就在初始值的基础上增加或减小一定的值;一个"确认"键,用于确认调节后的数据,按一下,选中通道的延时送入DS1023S-25;一个"取消"键,用于取消设置的延时数据,返回初始值。

#### 1.4 显示电路

延时分配器用液晶显示模块设计了显示功能,显示每个按键的动作及 4 路延时脉冲的延时时间。液晶显示模块是 128×64 点阵的图形液晶显示模块,能显示 16×8 个字符,内藏控制器<sup>[11]</sup>。单片机与液晶显示模块的连接有直接访问方式和间接访问方式两种。直接访问方式是将模块接口作为外部存

储器直接挂在单片机总线上,单片机以访问外部存储器的方式对模块进行操作;间接访问方式是单片机通过软件模拟控制时序对模块进行操作。延时分配器中,控制模块 C8051F340 与液晶显示模块采用直接访问方式连接,数据线和地址线分别与液晶显示模块的数据线和地址线相连,读写控制时序由单片机硬件完成,单片机的读写信号经过一个与非门与显示模块的使能脚连接,故程序简捷、速度快。

# 2 软件设计

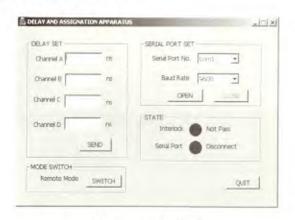

延时分配器的控制软件包括上位机程序和下位 机程序,上位机程序用 VC++语言编写,主要用于 遥控模式时远程计算机与延时分配器通信,发送延 时控制命令、显示状态参数等(图 3)。下位机程序即 单片机 C8051F340 的控制程序,用 C51 语言编写, 包括系统初始化、6 个按键的处理、LCD 显示以及 串口发送和接收数据。

图 3 上位机遥控界面 Fig.3 Computer remote control interface.

#### 2.1 上位机程序

遥控模式时,远程计算机通过 RS232 接口操作延时分配器,上位机程序操作串口,与单片机通信,发送和接收数据。发送的数据是"DELAY SET"部分,即 4 个通道的延时,按"SEND"按钮即开始发送;接收数据是延时分配器的联锁输入状态,用灯的颜色表示通过或未通过。在软件的设计过程中,要保证上位机和下位机进行准确可靠的通信,通信双方要遵循规定的通信协议,通信双方使用相同的波特率和统一的字符帧格式传送数据。单片机使用的波特率是 9600,则上位机程序也应选择 9600。发送数据的字符帧格式见表 1,下位机按这种格式接收并处理数据。接收数据的字符帧格式见表 2。

表 1 发送帧格式 Table 1 Frame format of send data

| 0xFF | 'A' | 数据     | 'B' | 数据     | ,C, | 数据     | 'D' | 数据     | 校验     | 0xFE |

|------|-----|--------|-----|--------|-----|--------|-----|--------|--------|------|

|      |     | A      |     | В      |     | С      |     | D      | verify |      |

|      |     | data A |     | data B |     | data C |     | data D |        |      |

0xFF: 帧头,表示一帧数据的开始,1个字节;0xFE: 帧尾,表示一帧数据的结束,1个字节;

A: 通道 A 延时数据起始标志, 1 个字节:

B: 通道 B 延时数据起始标志, 1 个字节;

C: 通道 C 延时数据起始标志, 1 个字节:

D: 通道 D 延时数据起始标志, 1 个字节;

数据: 延时数据,以字符形式表示,字节数由每个通道所设置的十进制实数的位数决定。

校验: 对除帧头帧尾外的数据进行偶校验的结果,1 个字节。

表 2 接收帧格式 Table 2 Frame format of receive data

| 0xFF | 数据   | 校验     | 0xFE  |

|------|------|--------|-------|

|      | data | verify | 5.4.5 |

0xFF: 帧头, 1 个字节;

0xFE: 帧尾, 1 个字节:

数据:表示联锁输入状态,1个字节;

校验: 对除帧头帧尾外的数据进行偶校验的结果, 1 个字节。

# 2.2 下位机程序

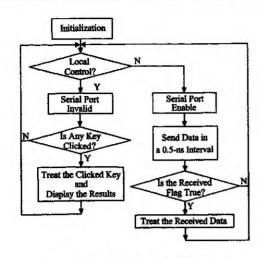

单片机 C8051F340 要在遥控模式时与上位机通 信,在本地模式时处理键盘输入和控制显示模块, 下位机程序的主流程如图 4 所示。延时分配器开机 后,进行系统初始化,主要包括与延时电路、键盘、 显示模块和串口相关的单片机内部特殊功能寄存器 的初始化,LCD 模块初始化。接着判断操作模式, 若为本地操作模式,则屏蔽串口,遥控操作无效, 接着扫描键盘有无键按下,若有,则处理该键的动 作,并同时在 LCD 屏上显示结果,扫描完 6 个键后 再判断操作模式。若为遥控模式则把串口连接到单 片机 I/O 口, 串口可以发送和接收数据, 面板键盘 无效。串口发送和接收同时进行,发送数据帧格式 如表 2, 每隔一定时间发送一帧。接收中断程序把 接收的数据保存到一个缓冲区,接收到帧尾后,标 志置位,然后主程序对缓冲区中的数据进行处理。 首先找到帧头帧尾,然后进行校验,校验不正确, 则把这一帧扔掉,正确则把各通道的字符数据变为 相应的数字数据,设置相应的延时芯片的延时,处 理结束判断操作模式。

图 4 延时分配器控制程序流程图 Fig.4 Program flow chart of the delay and assignation apparatus.

# 3 功能及测试

延时分配器实现 1 路主定时光触发脉冲输入,同步 4 路电触发脉冲输出; 4 路输出脉冲相对输入脉冲的延迟时间独立可调,延时可调范围 0-64 ns,最小调整步长 0.25 ns;每路输出脉冲的状态通过LCD 和 LED 指示灯显示(图 5);即可通过前面板键盘操作,也可通过 RS232 接口遥控,延迟时间调节实时、方便;具备联锁保护功能,且联锁输入信号状态以 LED 指示灯显示。

图 5 触发脉冲延时分配器 Fig.5 The trigger pulse delay and assignation apparatus.

输出脉冲的延时可调范围和调整步长由集成延时芯片决定,前沿上升时间和延时抖动与整个电路有关。经测试,由于 DS1023S-25 对输入脉冲的整形功能,输出脉冲的前沿上升时间小于输入脉冲的前沿上升时间,输入脉冲的前沿上升时间为 10 ns时,4 路输出脉冲在不同延时的前沿上升时间为2.5—4 ns。输入脉冲频率小于10 MHz 时,4 路输出脉冲在不同延时时的前沿抖动为70—100 ps。图 6 是用示波器测量的延时分配器输出脉冲的前沿上升时间和延时抖动。

图 6 输出脉冲性能测试(a) 前沿上升时间(b) 前沿抖动 Fig.6 Output pulse performance measurement: (a) rise time of forward edge, (b) jitter of forward edge.

# 4 结论

该延时分配器使用了先进的可编程延迟芯片,电路结构简单,参数设置方便,延时精度和准确度满足要求。1 路定时光脉冲输入,4 路延时独立可调快前沿低抖动电触发脉冲输出,输出脉冲最大可调延时 64 ns,调整步长 0.25 ns。采用单片机作为控制部件,带有全双工通信接口,可遥控操作,便于控制系统联网操作,适应 SSRF 的联调和调束控制操作。该仪器面板采用简化的键盘,本地操作简捷方便,工作状态由 LCD 模块显示,实现了工作状态可视化。软件模块化设计,功能易扩展。

# 参考文献

- 1 上海光源工程设计报告, 2000, 1: 4-19-4-23 SSRF Design Report, 2000, 1: 4-19-4-23

- Papastergiou G, Matakias S, Koukouvinos I, et al. SPIE, 1998, 3423(0277-786X): 107-111

- 3 Stanford Research Systems, MODEL DG535 Digital Delay / Pulse Generator, 2005, Revision 2.8: 23-27

- 4 高辉、陈文通、王金祥、等. 可编程器件在纳秒级多通

道数字延迟/脉冲发生器中的应用[J]分析仪器, 2002,(3) 13-17

GAO Hui, CHEN Wentong, WANG Jinxiang, et al. Application of programmable logic device in mult ichannel nanosecond digit al delay/ pul se generator [J] Analysis Instrument, 2002, (3): 13-17

- 5 刘英. 今日电子, 2003, (3): 17-19 LIU Ying. Electronic Products China, 2003, (3): 17-19

- 6 陈兴文,刘燕. 可编程宽频带精密延时器设计[J]. 微计算机信息, 2004, 20(9): 79-80 CHEN Xingwen, LIU Yan. Design of wideband precision programmable delay [J]. Micro Computer Information, 2004, 20 (9): 79-80

- 7 Antonio Ordine, Alfonso Boiano, Walter De Cesare, et al. IEEE transactions on nuclear science, 2004, 51 (5): 2947-

- 2956

- 8 徐锡林. AD9500 高速数字可编程延时发生器的特点及 其应用.[J]. 电子技术应用, 1997(11): 59-62 XU Xilin. AD9500 high-speed digital programmable delay generator characteristics and applications [J]. Electric Technology Application, 1997, (11): 59-62

- 9 Dallas Semiconductor, DS1023 8-Bit Programmable Timing Element, 062498, 1-17

- Silicon laboratories, C8051F340/1/2/3/4/5/6/7 Full Speed USB Flash MCU Family, 2006, Rev.1.0:1

- 11 内藏KS0108B/HD61202 控制器图形液晶显示模块使用手册, 北京精电蓬远电子有限公司, 2002, 6-26 Manual of Graph LCD Module with KS0108B/HD61202 Controller in It, Beijing Pengyuan Electronics Co., Ltd., 2002, 6-26

# The subnanosecond trigger pulse delay and assignation apparatus for storage ring injection at SSRF

DI Lanlan GU Ming YUAN Qibing FAN Xuerong

(Shanghai Institute of Applied Physics, Chinese Academy of Sciences, Shanghai 201800, China)

Abstract A trigger pulse delay and assignation apparatus, using an appropriative and controllable delay line chip, has been developed for SSRF storage ring injection system. With the input being one light pulse, and the outputs being 4 electric pulses, the delay is independent and adjustable, and the rise time is short and jitter is low. The delay is 0.25-ns steps, with an adjustable range of up to 64 ns. In addition to the function of pulse delay, the apparatus also has the interlock function and LCD display. It can be operated on keyboard, and can be controlled remotely through its serial port.

**Key words** Subnanosecond, Delay and assignation apparatus **CLC** TN786