www.scichina.com

info.scichina.com

# 纳米 CMOS 工艺下集成电路可制造性设计 技术

## 程玉华

北京大学上海微电子研究院, 上海 201203

E-mail: chengyh@pku.edu.cn

收稿日期: 2008-01-10; 接受日期: 2008-04-09 国家自然科学基金资助项目(批准号: 60736030)

摘要 简要讨论纳米 CMOS 工艺下集成电路的可制造性设计 (DFM)技术. 首先讨论纳米 CMOS 中与制造性有关的工艺和器件 问题, 然后探讨 DFM 需要的工艺和器件建模工作. 最后对包括有可制造性设计技术的集成电路设计流程和能较好地在大规模集成电路设计环境中开发设计/制造交互界面的有关 EDA 做简单介绍.

#### 关键词

可制造性设计(DFM) 基于成品率的设计 纳米 CMOS 集成电路设计 集成电路设计方法学 CMOS 设计技术平台

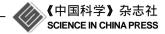

随着生活水平的持续提高和全球经济的稳定发展,对于小尺寸、低价格和低功耗的电子产品的需求急剧增加. CMOS 集成电路可以实现这些目标,从而被广泛应用于各商业电子产品,因而推动 CMOS 技术不断向先进工艺节点发展直到目前的纳米工艺技术阶段. 纳米工艺所制造的芯片上晶体管数量大大增加,极大地改进了芯片性能且减小了制造成本,这使得纳米尺寸 CMOS 集成电路成为实现系统集成最具吸引力的技术. 然而如图1所示,纳米工艺下电路设计(包括设计工具和掩膜制造)的成本大大增加. 这样,一次性流片成功从而节约成本便成为对芯片设计者的基本要求. 此外,如何改进芯片的成品率,已经不再仅仅是芯片制造者的责任,现在也转移到了芯片设计者的肩上. 如何提高成品率的问题必须在芯片设计的早期就要考虑.

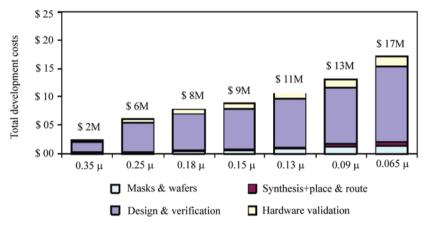

传统上,芯片成品率取决于电路设计过程中遵循设计规则的程度. 当工艺节点(晶体管的特征尺寸)向更小尺寸迈进,这种方法带来了许多问题. 在旧的工艺节点(0.18 μm 及以上)中,电路设计规则很简单,仅用几页纸的设计手册即可将其定义和解释清楚. 但是,先进工艺(0.13 μm 及以下)节点下的电路设计规则爆炸性地增加了 5 到 10 倍,甚至有些时候某些设计规则之间本身就相互冲突.在 65 nm 和 45 nm 工艺节点下情形则变得更加复杂.在纳米尺度技术节点下,成品率改进的问题并不能完全由所谓的"光学临近效应修正(OPC)"和"相移掩膜(PSM)"等技术解决,要求更精确地预测制造中可能出现的问题.此外,随着器件尺寸不断地缩小,晶体

管表现出与微米尺度工艺节点下不同的电学特性.如图 2 所示,工艺参数、制造环境参数的剧烈波动,与随机效应一起成为成品率增强需要考虑的关键因素.

图 1 进入纳米CMOS工艺后设计成本逐渐增加<sup>11</sup>

图 2 工艺变异、系统和随机缺陷等成为高级技术节点下影响芯片成品率的关键因素[2]

当前的大部分设计工具只能处理静态效应. 然而, 纳米领域工艺和器件的效应更具有统计性, 需要以概率分布来描述<sup>[3,4]</sup>, 这增加了芯片制造的不确定性, 使得成品率控制更加困难. 为了降低设计成本与缩短产品投入市场时间, 我们需要能够把所有关键因素(比如成品率、工艺/器件波动性、功耗、芯片面积、时序和性能等)考虑进去的更好的设计工具. 由此我们可以在满足成品率的前提下优化芯片性能、面积和速度. 成品率已经成为除低功耗和高集成度之外的先进的电路设计中的关键问题之一.

同时,由于传统的设计方法不能满足纳米 CMOS 集成电路设计的需求,纳米尺度工艺节点下的集成电路设计方法已经发生了根本性的变化. 芯片设计者和制造者的分界已经变得模

糊,且在电路设计流程中设计技术和工艺技术间的信息交换变得非常关键. 电路设计、EDA 和芯片制造的角色变得不再清晰可分. DFM 技术已经成为 65 nm 及以下工艺节点下集成电路设计"必须"具备的关键工具. 包含了 DFM 技术的新设计方法和设计流程的详细研究非常重要.

因DFM涉及了版图设计、工艺建模、器件建模、电路设计技术、系统架构以及集成和测试/封装等方面的许多基本物理问题[5-8],所以DFM的研究需要工业界和学术界的共同努力,以分析、理解和解决这些问题来满足产业发展的要求。最近,许多芯片制造商如TSMC和UMC等与EDA公司如Cadence和Synopsys等都在研究开发DFM技术和新的设计流程(www.umc.com, www.tsmc.com, www.cadence.com, www.mentor.com, www.synopsys.com, www.magma-da.com),以改善现在的设计环境,并且精确预测由于生产过程中的工艺参数变化而引起的器件特性的随机变化。完整的集成电路设计流程最终将由"设计收敛"转移到"制造收敛"。DFM观念正在进入电路设计的每个阶段,通过EDA工具的帮助来提高成品率。按照EDA领域一些专家的观点,纳米尺度工艺技术下的设计方法不仅要保证所设计电路的性能,而且要提高设计的可制造性,同时具有预测产品性能和成品率的能力。由于在纳米工艺技术下对各种效应和问题的探索尚处于基础研究阶段,对DFM/DFY技术及将其与设计流程集成的研究还处于早期。到目前为止,只有TSMC和UMC发布集成了DFM技术的 65nm设计流程(www.umc.com, www.tsmc.com).

本文将综述纳米 CMOS 工艺下 IC 设计中 DFM 技术的研究现状. 我们首先将讨论先进工艺技术节点下与集成电路可制造性设计相关的工艺/器件问题. 然后探讨为可制造性设计技术服务的先进工艺/器件建模问题. 我们的讨论还简单涵盖了旨在更好解决超大规模集成电路设计环境中的设计-制造衔接问题和具有 DFM 意识的设计流程以及先进 EDA 技术.

#### 1 与成品率相关的工艺和器件问题

IC 制造工艺本身就是有缺陷的,温度、工艺步骤持续时间、掺杂浓度等等的差异导致晶圆之间、同片晶圆上的裸片之间和同一裸片上晶体管之间的器件性能有所差异. 关键尺寸的控制和工艺的波动性向制造和设计提出了挑战,一些效应如泄漏电流和功耗等成为纳米尺度下CMOS 集成电路设计需要考虑的严重问题.

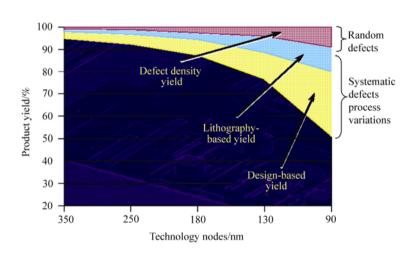

如图 3 所示,随着CMOS进入先进工艺技术节点,沟道和栅端的泄漏电流急剧增加.泄漏电流(包括亚阈值漏电、栅漏电、结漏电和带带隧穿漏电等)成为 65 nm和 45 nm节点产业界的主要关注因素.若不采用高一k材料时,器件的性能的提高需要更薄的栅氧化层,这导致每个工艺节点下单位栅宽的泄漏电流增加了一个数量级.泄漏功耗不仅是能源的浪费,而且对可实现的波形因数、集成度、封装的选择、可靠性和产品的其他性能都会产生影响.而且,工艺波动性对泄漏电流的影响是非常大的,漏电的大小与关键尺寸如晶体管的栅长(也就是沟道长度)成反比且呈指数上升,来自同一批晶圆的芯片之间总的漏电可以有 5 倍到 20 倍的变化.通过采用多阈值电压技术(MTCMOS),或者更高级的设计技术来减小泄漏电流将导致面积增大和设计步骤复杂而且引入更多的不稳定性(随机掺杂的涨落、在将来的技术节点中电源电压的减小致使多阈值技术可行性减小)<sup>[8]</sup>.

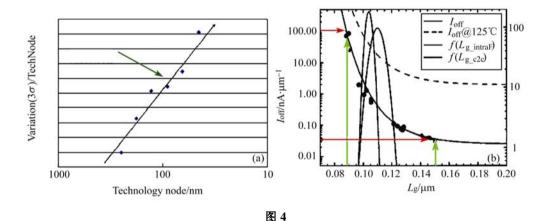

在较先进的技术节点下,随着芯片上器件关键尺寸(CD)的缩小, CD 波动变得更大(如图

4(a)所示). 小的物理波动会导致大的电学波动,例如,当沟道长度(L)为微米量级时,一个晶体管相对另一个晶体管沟道长度 L的微小波动只有相对较小的影响,对比而言,因为纳米工艺中器件 L 小于 100 nm, L 的微小波动将导致电学参数诸如漏电流等的变化很大,如图 4(b)所示.

图 3 随着 CMOS 工艺技术发展,漏电流极大增加

(a) 沟道漏电流; (b) 栅漏电流

(a) 先进工艺技术节点下的关键尺寸(CD)波动性变大; (b) 0.13 µm 工艺下关键尺寸(CD)波动导致漏电流成数量级地变化

晶圆制造中一系列的化学机械抛光(CMP)步骤是导致器件参数波动的一个主要原因之一(www.magma-da.com). CMP会导致晶圆表面和裸片表面连线厚度的不均匀,不同技术节点下 CMP 导致的波动绝对值的大小几乎一样. 由于 65 nm 工艺节点的连线关键尺寸(包括宽度和高度)比 90nm 工艺节点要小,相同厚度的波动性在 65 nm 工艺节点造成的偏离百分比要大. 可以通过增强金属密度规则来防止灾难性失效,但是仍会对电学性能的重要参数产生严重影响. 在较先进的工艺技术节点中,光刻是导致工艺制造波动性的最主要成因.

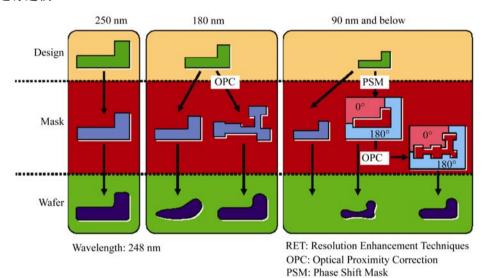

图 5 举例说明了在纳米尺度 CMOS 工艺下光刻工艺步骤如何影响器件性能和成品率. 真正的问题在于芯片的特征尺寸小于用来形成这些图形的光波波长. 如果黄色区域的几何图形

是在不同工艺节点下所画的版图,在 0.25 μm 及以上的工艺中,可以由常规的物理设计工具产生版图,以进行掩膜制造(如图红色区域所示).问题是如果这个图形是在诸如 90 nm 及以下等更高级工艺节点下的光掩膜下复制,那么随着新技术节点图形尺寸的持续减小,在硅片上得到的实际图形与理想图形的偏差会越来越大.当前采用的方法是在常规的设计流程中对GDSII 文件进行分辨率增强技术(RET)的后处理如 OPC 和 PSM,但是这会对时序变化、噪声、功耗、以及最终的成品率等产生影响.真正具有 DFM 意识(DFM-aware)的解决方案,必须解决所有这类问题,这意味着必须在电路实现、分析、优化和验证等过程中将所有系统的和随机的效应进行建模.

图 5 更高级工艺技术节点下版图图形与实际硅片上图形差异对比(www.synopsys.com)

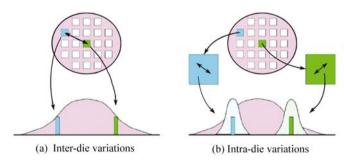

90 nm 及以下工艺中的另一个重要问题是芯片间的波动性变得很大. 这意味着位于晶圆中心的芯片可能和位于晶圆边缘的芯片表现出不同的性能,如图 6 所示(www.magma-da.com). 在这种情形下,水平的 x 轴表示和中心值的偏差,垂直的 y 轴表示 x 具有相应值的概率,这就是所提到的概率密度函数(PDF). 因此,需要在设计过程中针对芯片间的波动性多方面地对具体设计进行优化分析.

图 6 90 nm 及以下技术节点的裸片间变异与裸片内变异(www.magma-da.com)

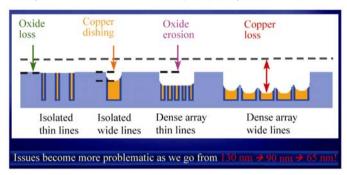

更糟糕的是由于刻蚀和化学机械抛光(CMP)等工艺步骤可导致芯片内部产生较大的波动性. 比如,刻蚀工艺的不一致会导致裸片中部分区域的连线比其他区域的宽些. 同样地, CMP工艺问题,如图 7 所示,可导致金属和绝缘层厚度的变异,从而引起 IR 压降效应和散热问题.

图 7 使用铜互连的 0.13 µm 及其以下工艺中的 CMP 问题(www.umc.com)

为了确保硅片表面的平坦化,一种方法是使用金属填充和金属线开槽来获得均匀的互连线图形和减小形貌的波动性(也就是互连线电学性能的波动性).制造者已经开发了确保满足成品率和生产需求的用于金属填充和金属开槽的设计规则.然而,这些规则常常有很多问题,比如,用于生成金属填充和金属线开槽的算法不是满足制造和设计效率的最优化算法;而且一旦金属填充之后很难对数据库进行设计规则检查.并且,金属填充和金属开槽对延迟、串扰、电路 RF 性能的影响很难进行量化分析.目前,基于设计规则的金属填充和金属开槽方案可以在设计阶段,或者在制造厂或者在掩模版厂采用.然而,随着几何尺寸的缩小设计规则需要具有将厚度波动减到最小的能力.同时,开发智能的金属填充算法是一项复杂而具有挑战性的任务,算法需要对测试芯片上的各种设计产品进行测试,由于制造和设计相关的资源问题,很难完成这一闭环流程.金属填充的算法一旦建立,工艺开发者便不想改变它,以避免由于需要确定算法变化而付出的大量工作,包括反复的金属填充实验、晶圆制造和对每个测试结构的测量等.经常,尤其是在模拟和射频电路设计中,由于与金属填充有关的电学特性的不确定性,设计者需要把芯片上金属层某个部分的特殊区域和金属填充区进行隔离以将潜在的影响减到最小.在65 nm 和45 nm 的技术节点中,具有精确互连厚度波动预测的智能金属填充和金属开槽方案可以减小或消除设计中的不确定性,因此在下一代技术平台中是必需的.

为解决这些问题,我们必须借助统计效应,这意味着使用伪随机变量(而不是确定值)并且 重新产生这些统计效应.统计分析将会大大减小时序分析运行的次数,从而减小设计周期,并 可更好的满足时序、功耗、噪声以及成品率等设计目标.

## 2 用于 DFM 技术的工艺/器件建模

工艺/器件建模是工艺技术和设计者之间的一个关键连接纽带. 理想情形下, 对于所有的工艺步骤和器件效应, 包括工艺和器件中的寄生效应, 都应该进行建模. 从而设计者可以使用这些模型运行仿真, 以在流片前对电路表现进行精确预测. 尽管在实际中很难做到这一步, 但

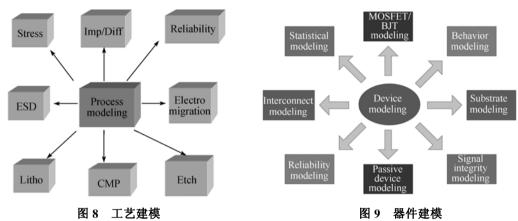

是作为设计技术平台的基础,针对 DFM 应用的精确、有效的工艺/器件建模,应该认真而且尽可能全面地加以完成.工艺建模应该包括主要的工艺步骤,如光刻、CMP、刻蚀、离子注入/扩散以及应力的影响、电迁移和可靠性等,如图 8 所示.器件建模应该包括有源元件(MOSFET和 BJT)、无源器件(电容、电阻、电感和变压器)、互联线和衬底寄生效应建模、封装建模、以及模块级的功能建模等(如图 9 所示).此外,如前面所提及的,由于和版图形状有关的应力效应、光刻和刻蚀引起的几何尺寸的波动等因素,统计建模是该模型框架的必不可少的另一部分.

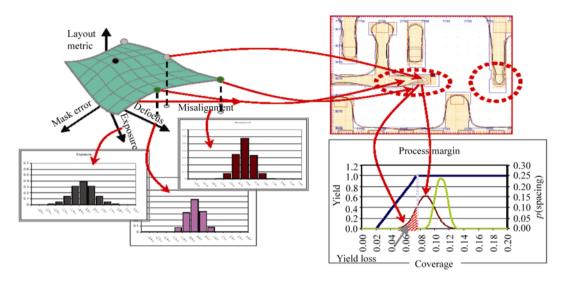

为开发用于 DFM 的工艺模型,需要探索新的建模技术.业界(www.pdf.com)论述了一种包括几何图形和统计效应的建模方法,如图 10 所示.

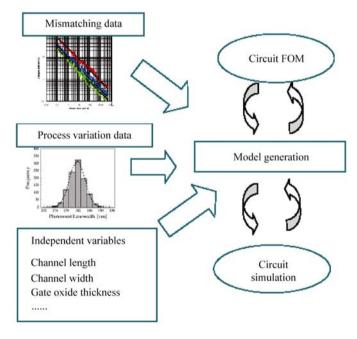

随着工艺技术的进步,为了开发满足 DFM 应用的更好的工艺/器件模型,诸如用于全局工艺波动性和局部失配的统计建模等高层次建模变得很重要. 纳米尺度工艺节点下的模型除了包括基于传统的"corner case"(最差/最好情形)概念的传统紧凑模型之外,还需要具有不同器件"Figure-of-Merit"的统计模型的补充. 为了预测工艺波动性和器件失配对器件性能的影响,独立工艺/器件变量的选择和独立变量相关连接的建立,以及器件的模型参数间相关性的产生是最重要的. 在考虑最重要的物理效应以及独立工艺变量间的相关性的同时,模型必须很好地预测工艺波动性和失配行为对不同偏置情形下不同几何尺寸的器件的影响. 在 SoC 设计技术平台中,精确的物理统计模型在 SoC 设计技术平台中是很重要的组成部分,用来正确的预测和优化电路性能(如: 功耗、时序、噪声和增益等). 图 11 给出了统计建模的一个概念性流程.

信号的完整性分析,主要是由串扰或者 IR 压降引起,是 DFM 技术应包括的一个重要方面. 串扰能引起信号延迟的波动,导致时序错误或者是违背设计意图的短时脉冲波形干扰从而引起功能失效. IR(电压)降由电源线上直流电压波动性引起,成为当前电路设计中一个严重问题,因为在 0.13 μm 及以下工艺尺寸中, IR 降能诱导芯片时序的改变. 忽略信号的完整性效应会引起逻辑或时序问题,从而导致功能失效或者性能降低. 互连/衬底建模是信号完整性分析和模拟中的重要部分,互连的寄生效应和衬底噪声耦合引起的延迟应该在信号频率的全频带内予以考虑分析. 精确而高效的互连模型在纳米尺度设计中非常关键,互连问题和衬底噪声占到

图 10 基于版图信息的成品率模型(www.pdf.com)

图 11 用于 DFM 的统计性器件建模

电路可靠性和信号完整性问题的 30%以上. 对互连和衬底寄生效应建模主要的挑战在于提供精确而高效的 RLC 计算结果,并预测互连/衬底寄生效应的影响以及把这些寄生效应物理上联系起来对延迟、串扰、IR 降、功耗进行分析. 此外,这些寄生效应对 RF 电路单元的影响应该予以合理的评估,目前,因为不同的工具对电路电学参数分析侧重点不同,人们使用不同的工具来评估这些寄生效应对数字和 RF 电路的影响. 然而人们更加倾向于同一个工具能够分析不

同应用场合的各种寄生参数的影响. 另一个例子是衬底的建模和仿真, 在 SoC 设计中衬底成为一个主要的关注因素, 数字电路可能对衬底注入脉冲信号, 这个信号可能被一些敏感电路如 RF 模块俘获, 衬底耦合噪声也需要进行精确的建模和仿真.

如前面提到的,3项DFM技术(金属填充、金属线开槽以及OPC)已经被广泛应用来增强均匀性.但是由于芯片内部的波动性,也就是对于晶体管和互连仍有显著影响的片上波动性(OCV),这3种方法不足以解决所有DFM有关问题.除了OCV,还有显著的芯片间的、晶圆间的、不同批次晶圆间的波动性,对成品率都会产生负面影响.对铜互连而言,OCV被认为是影响成品率的最主要因素,所以对晶体管和互连的OCV建模是必需的.在实际应用中,晶体管波动性的建模方法应该与互连线波动性的建模方法相结合[9].

### 3 具有 DFM 意识的设计流程

DFM 已被认为是在纳米尺寸技术节点下设计者进行设计、验证、流片和封装测试等每一阶段为可制造性而进行电路优化所需要的关键技术步骤. 一个好的 DFM 技术具有可以定性设计相关目标布局所需工艺的能力,并定义那些为取得目标布局而采用的最佳分辨率增强技术.它应该包括在版图制造级和工艺级的详细模型,在此基础之上发展所谓的基于模型的物理验证. 综合、布局布线、单元设计、寄生参数提取、物理验证和芯片测试等都需要加入 DFM 功能. 基于嵌入式 DFM 技术的设计流程包括对缺陷及其影响的深入了解,从而针对在此工艺节点下的设计开发出修正和分析的方法,同时需要了解上自设计下至测试相关的制造工艺和设计工具. 众所周知, DFM 已经成为全芯片的问题,在芯片中引入一个在可制造性问题没有经过确认的电路单元可能会对整个芯片的可制造性产生重要的影响. 具有自动优化技术的全局DFM 技术可以高效地衔接整个产品设计流程. 这需要芯片制造商、EDA 供应商和设计人员的共同努力来开发一种成熟、全面而有效率的设计流程.

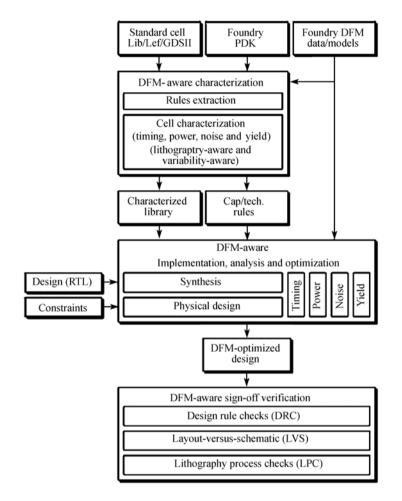

在集成电路设计中, DFM 被广泛通过诸如 OPC 和 PSM 等各种分辨率增强技术(RET)用于对 GDSII 文件进行光刻增强技术后处理. 在 65 nm 及以下技术节点芯片制造中这将不再可行. 为了得到可接受的性能和成品率,如图 12 所示,整个设计流程应该具有 DFM 意识. 这包括:具有 DFM 意识的描述表征、具有 DFM 意识的实现、分析和优化,以及具有 DFM 意识的签字确认.

物理验证变得比以往任何时候都重要,因为纳米尺度 IC 的实现呈现出更多信号完整性相关的问题,所以为避免芯片功能失效必须进行充分的验证分析. 在纳米尺度 IC 中,除先进工艺技术所要求的越来越复杂的验证程序之外,发现设计中或者最后的设计调整中遗漏的各种问题也已成为一项挑战任务. 理想情形下,所有的问题(IR 压降、串扰、时序和功耗等)都应该在早期发现来避免推迟"芯片出带(Tape-out)"时间. 设计实现中用来帮助设计收敛的工具应该足够的高效、灵活,在没有对设计的性能、功耗、面积进行大量折衷的基础上提供电学完整性的分析和指导帮助,以维持其设计效率. 这种适用于 3D 寄生参数提取、全芯片 IR 压降分析、全芯片串扰分析、以及具有信号完整性意识的静态时序分析功能的集成工具,应当经过实际生产的证明以及实际硅片验证. 虽然现在商业 EDA 工具提供了一些解决方案,但并不是所有类型的设计都能得到有效地验证. 尤其是当涉及到具有很大数据量的大型纳米 SoC 电路时.

图 12 一种具有DFM意识的设计流程示意图 (www.magma-da.com)

OPC和PSM等分辨率增强技术的大量应用极大地增加了纳米尺寸下光掩膜的成本和复杂性. 光掩膜图形不再是设计版图图形的精确复制. 结果, RET 综合精确性的可靠验证、结构的完整性、掩模制造规则的一致性成为纳米尺度设计电路制造中的关键问题. 除广泛应用的基于规则的验证方法之外, 业界一直在努力开发更好的验证技术, 因为物理验证已经成为完成高效而可靠电路设计的瓶颈. 其中一种是基于模型的验证方法, 比如, 一个基于模型的掩膜验证技术能验证出用于掩膜校正的版图问题, 并且预测晶圆光刻中可能出现的错误.

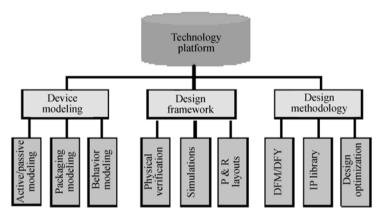

为对设计的每个阶段提供一个完整的流程,需要开发出可靠和先进技术支持的系统.这个流程可称之为技术平台,如图 13 所示.该平台将会集成所有的技术环节,包括器件模型、验证、各级别上的仿真、不同应用的 IP、封装设计、DFM 和具有成品率优化考虑的自动布局布线等等.系统和电路级的设计方法需要在设计的不同阶段,如系统设计和体系结构的定义、电路级设计和仿真、物理版图、器件和电路设计规则检查、物理与逻辑的设计对比、信号完整性、时序收敛、功耗与性能的折衷与优化等,引入很多的 CAD 工具.设计框架使用设计数据库将这些 CAD

工具联系起来.设计框架的重要性在于可将不同供应商工具集成在同一个设计环境中以及其开发实用性和增强性定制软件的能力.芯片电路设计者通过这个包含了诸如器件模型等所有构成单元的设计框架而获取工艺技术.设计框架还包含另一些在芯片级关键单元,如图形获取、版图、物理验证工具、用于时域和频域分析的仿真工具,以及互连寄生参数提取/建模的工具等.系统设计者可在设计框架的不同层次来处理芯片模块的时序收敛、功率以及性能等问题.

图 13 集成电路设计技术平台示意图

## 4 总结

本文讨论了纳米 CMOS 技术下集成电路的可制造性设计的有关问题. 在理解和探索纳米尺寸 CMOS 技术可制造性相关的大量基础的工艺/器件问题方面还有很多的工作要做. 应当开发为可制造性设计服务的工艺/器件建模新技术, 以满足现代 SoC 设计的需要. 具有 DFM 意识的设计流程已经成为 65 nm 及以下技术节点集成电路设计必需的工具环境. 在超大规模 IC 设计环境中, 为更好地处理设计一制造之间的许多问题, 需要大量的 EDA 技术有关的重大突破.

#### 参考文献

- 1 Maly W. IC design in high cost nanometer technologies era. In: Proceeding of Design Automation Conference. Las Vegas. IEEE Solid-state Circuit Society. 9—14

- 2 Fichtner W, Pramanik D, Bomholt L. Closing the gap between manufacturing and design. 2005 Electronic Design Process Symposium. Monterey California. IEEE Solid-state Circuit Society. 64—68

- 3 Sifri J. Statistical design can increase IC yield. In: EETimes, 02/24/2003

- 4 Burek D. True design-for-manufacturability critical to 65-nm design success. In: EETimes, 11/07/2007

- 5 Verghese N, Hurat P. DFM reality in sub-nanometer IC design. 2007 Asia and South Pacific Design Automation Conference, 2007, Jan. 23-26, Pacifico Yokohama, Yokohama, Japan. IEEE Solid-state Circuit Society, 226—231

- 6 Guardiani C, Dragone N, McNamara P. Proactive design for manufacturing (DFM) for nanometer SoC designs. In: Proceedings of the 2004 IEEE Custom Integrated Circuits Conference, 2004, 3-6 Oct, San Jose, California. IEEE Solid-state Circuit Society, 309—316

- Kibarian J. Enabling true design for manufacturability. Sixth International Symposium on Quality of Electronic Design, 26-28 March 2007, San Jose, CA, USA. IEEE Computer Society. 15

- 8 Kahng A B. Design challenges at 65 nm and beyond. 2007, Design Automation & Test in Europe Conf. & Exhibition, 2007, April 16-20, Nice, France, IEEE Computer Society. 1—2

- 9 Chang K J. Accurate on-chip variation modeling to achieve design for manufacturability. In: Proceedings of the 4th IEEE International Workshop on System-on-Chip for Real-Time Applications (IWSOC' 04), 2004, July 19-21. Banff, Alberta, Canada. IEEE Circuit and System Society, 219—222