www.scichina.com

info.scichina.com

# 测试技术专刊 论文

# 基于脉宽收缩和累积寄存器的片上时钟抖动测试 电路

冯为蕾<sup>①</sup>, 冯建华<sup>①②\*</sup>, 叶红飞<sup>②</sup>, 张兴<sup>①②</sup>

- ① 北京大学深圳研究生院, 深圳 518055

- ② 北京大学微电子学研究院, 北京 100871

- \* 通信作者. E-mail: fengjh@pku.edu.cn

收稿日期: 2014-05-20; 接受日期: 2014-08-14 国家自然科学基金 (批准号: 61176039) 资助项目

摘要 本文提出一种基于脉宽收缩和累积寄存器的片上时钟抖动测试电路,用于监测片上时钟信号的抖动,测量精度可达到亚门级. 该测试电路是由脉宽收缩环路、累积寄存器、异或阵列、计数器和控制电路组成的. 以环形方式连接脉宽收缩单元,可减小由于工艺波动带来的影响,节省面积开销.在监测模式下,累积寄存器同时记录多个时钟周期脉宽的测量结果,并以数字序列码的形式输出,能够直观地显示时钟的抖动. 该电路是采用 65 nm CMOS 工艺设计的,仿真结果表明该电路可测量数 GHz 的时钟信号,测量精度为 1 ps.

关键词 脉宽收缩 时钟抖动 片上测量 抖动测试 累积寄存器

# 1 引言

近年来,随着集成电路的发展,器件的工作速度变得越来越快.目前,芯片的时钟频率一般可达到数 GHz,高速串行口的数据传输速率 [1] 甚至达到了 20 Gbps,速度的提高能够极大地改善电路性能,但同时信号抖动产生的影响也会变得越来越严重.在时序电路中,时钟抖动可能会使信号的建立和保持时间达不到要求,导致电路出现错误.在高速串行 I/O 中,时钟抖动会增加数据传输的误码率等 [2,3].因此,抖动已成为高速电路设计中面临的关键问题之一,其测量也是至关重要的.

目前测量时钟抖动的主流方法是片上测量法,该方法具有测量精度高,测量成本低和测量范围广等的优点,是近年来研究的热点.其中基于延迟链的测量方法 [4,5] 是最先提出的片上抖动测量法,该法原理简单,可进行实时测量,但最大的缺点是测量精度只能达到门延时量级,而且面积开销比较大,工艺波动也会导致延迟单元不匹配;游标卡尺延迟链测量方法 [6~8] 是从电路设计方面提高精度的,能够达到亚门级测量精度,该法同样可以进行实时测量,但延时链路依然增加了面积开销,也无法降低工艺波动对延迟单元造成的影响,而且测量所需的参考信号本身也会引入误差;游标卡尺振荡环测量方法 [9,10] 能够同时解决面积开销和不同单元工艺波动的问题,测量精度也是亚门级的,但无法进行实时测量,且参考信号本身的抖动也会增加测量误差;相位内插测量方法 [11] 的测量精度会受到寄生电容的影响,而且不能进行实时测量,其面积开销也比较大;时间放大测量方法 [12,13] 虽然可以实时测量,

引用格式: 冯为蕾, 冯建华, 叶红飞, 等. 基于脉宽收缩和累积寄存器的片上时钟抖动测试电路. 中国科学: 信息科学, 2014, 44: 1216-1225, doi: 10.1360/N112014-00147

但是测量精度受电容影响非常大,而且采用电容同样会增大面积开销; 脉宽收缩测量方法 [14~17] 也能达到亚门级测量精度, 该方法最大的特点是不需要参考信号就能完成测量, 因此不会增加测量误差, 而且能够节省面积开销, 减小工艺波动带来的影响.

综合分析上述时钟抖动测量方法可知,使用脉宽收缩法测量抖动会在测量精度,测量误差和面积开销等方面有较大的优势,但传统的脉宽收缩法得到的测量结果仅仅是单个周期时钟的脉宽测量结果,无法直接输出多个周期时钟抖动的总体情况.针对这个问题,IBM 提出一种同或处理电路 [18],结合逻辑门和触发器,可以输出多个时钟周期总体抖动的情况.本文将基于脉宽收缩测量方法和累积寄存器,设计一种能够直接输出总体抖动的时钟测量电路,并且测量精度以及测量范围均能满足数 GHz 信号抖动测量的要求.

# 2 电路设计与原理分析

# 2.1 脉宽收缩原理

在 CMOS 反相器中,由于输出节点总会存在容性负载,当输入信号发生跳变时,输出信号无法立即随之变化,而需要一定的响应时间,即上升时间  $t_r$  和下降时间  $t_f$ ,它们的表达式如式 (1) 所示,其中  $\mu_{(P(N)eff)}C_{ox}$  是常量, $C_L$  是输出负载, $V_{DD}$  是电源电压.因此,在保证负载和电源电压不变的情况下,可通过改变宽长比来调节上升时间  $t_r$  和下降时间  $t_f$ .

$$t_r = \frac{2C_L}{\frac{W_P}{L_P} V_{\text{DD}} \mu_{\text{Peff}} C_{\text{ox}}}, \quad t_f = \frac{2C_L}{\frac{W_N}{L_N} V_{\text{DD}} \mu_{\text{Neff}} C_{\text{ox}}}.$$

(1)

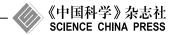

一般情况下,为了保证信号的对称性,电路设计要使上升时间和下降时间相等,信号经过反相器时还能保持原来的占空比,这样可提高电路性能.如果将反相器的上升时间和下降时间设计为不相等,那么信号通过一个由该反相器构成的缓冲器 (即脉宽收缩单元) 时,就会改变脉冲宽度 (一般是减小),最终减小的时间与两反相器的上升,下降时间之间的关系如图 1 所示.

由图 1(a) 可知, 当脉冲信号通过第一个反相器时, 由于器件的上升时间大于下降时间, 使得脉冲宽度减小了  $t_{PLH1} - t_{PHL1}$ ; 同理, 当信号通过第二个反相器时, 脉冲宽度减小了  $t_{PHL2} - t_{PLH2}$ , 如图 1(b) 所示; 那么当脉冲信号通过单级脉宽收缩缓冲器时, 如图 1(c) 所示, 最终减小的时间  $t_s$  为

$$t_s = t_{\text{PHL3}} - t_{\text{PLH3}} = t_{\text{PHL2}} - t_{\text{PLH2}} + t_{\text{PLH1}} - t_{\text{PHL1}}.$$

(2)

将式 (1) 代入 (2), 并化简得

$$t_{s} = \frac{2C_{L}}{V_{\text{DD}}} \left( \frac{1}{\frac{W_{N}2}{L_{N}2} \mu_{\text{Neff}} C_{\text{ox}}} - \frac{1}{\frac{W_{P}2}{L_{P}2} \mu_{\text{Peff}} C_{\text{ox}}} + \frac{1}{\frac{W_{P}1}{L_{P}1} \mu_{\text{Peff}} C_{\text{ox}}} - \frac{1}{\frac{W_{N}1}{L_{N}1} \mu_{\text{Neff}} C_{\text{ox}}} \right).$$

(3)

由式 (3) 可知, 单级脉宽收缩缓冲器减小的时间  $t_s$  主要由 4 个变量决定, 每个变量可通过改变相应 MOS 管的宽长比来单独调节, 因此具有很强的设计灵活性. 此外,  $t_s$  也与负载  $C_L$  成正比, 与  $V_{DD}$  成反比.

将多个相同的脉宽收缩单元串接起来形成链路,每个单元减小的时间都为  $t_s$ ,即最低有效时间  $T_{LSB}$ ,那么脉宽为 T 的时钟信号通过一级收缩单元时会减小一个  $T_{LSB}$ ,通过  $T/T_{LSB}$  级链接单元后就会彻底消失,此即脉宽收缩法测量时钟脉宽的基本原理,其分辨率由  $t_s$  决定,因此该方法具有很高的测量精度.

Figure 1 The principle of one stage pulse-shrinkage

#### 2.2脉宽收缩 TDC 环路设计

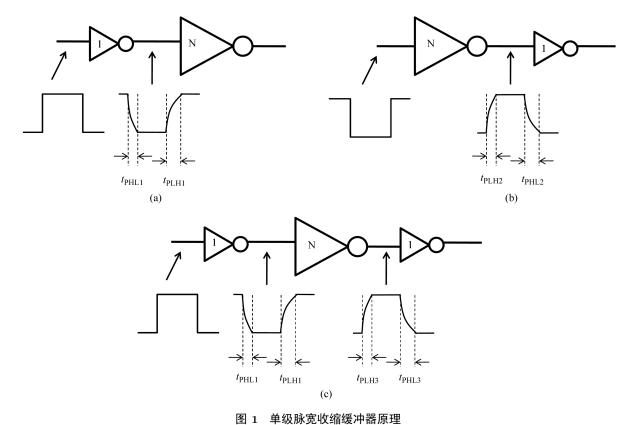

如果脉宽测量电路采用简单的串接方式,一方面会增加硬件开销,另一方面测量精度受工艺波动 的影响比较大, 因此并不是最佳的连接方式. 本文设计的脉宽测量电路采用环状连接方式, 同时用计 数器和触发器记录测量结果, 实现脉宽的时间 - 数字 (TDC) 转换, 其结构如图 2 所示.

每个收缩单元进行首尾连接形成环路, 采用计数器来记录循环次数, 每级收缩单元的输出接到 D 触发器的时钟端, 由于 D 触发器的输入端固定接 "1", 且每次循环开始之前都进行复位 (高电平有效), 故只要环路中存在脉冲, 就有触发器的输出由 "0" 变为 "1", 只有脉冲消失后, 触发器的输出才保持 "0". 测量开始之前, Reset 信号先置零, 再保持高电平, 然后输入待测脉宽, 如果脉宽经过 N 级收缩单 元后还没消失,将重新经过第一级收缩单元,同时计数器加1,触发器复位,直到脉冲消失.计数器的结 果和触发器的最后状态记录着脉冲通过收缩单元的个数 m, 其计算公式为

$$m = \operatorname{cnt} \cdot N + n_{\text{rest}},$$

(4)

其中 cnt 是循环的次数, 由计数器得出, N 是环内收缩单元总数,  $n_{\text{rest}}$  是触发器记录的最后状态下 "1" 的个数.

在图 2 所示的脉宽收缩 TDC 环路中, 单元级数 N 的选取与测量精度和测量范围都有着密切的 关联. 由图可知, 各级收缩单元的输出负载并不相等, 最后一级的输出负载最大, 故该级的  $t_s$  也是最 大的. 为了使各级收缩单元具有相同的  $t_s$ , 需要在前面 4 级的输出接入一定的负载 (如一定数目的 晶体管), 使每级输出负载与最后一级的负载相等. 由以上分析可知, 脉宽收缩环的测量精度是由最后

图 2 脉宽收缩单元环路连接

Figure 2 The loop connection of pulse-shrinkage units

一级收缩单元的  $t_s$  决定的,因此,为了提高测量精度,最后一级收缩单元所接的负载越小越好,即环路内的单元级数 N 越少越好. 另一方面,为了正确测量脉宽,要求输入信号脉宽  $T_{\rm in}$  小于环路完成一次循环的时间  $T_{\rm cycle}$ ,故  $T_{\rm cycle}$  就是电路的测量范围,环路单元级数越多, $T_{\rm cycle}$  就越大. 因此,为了增大测量范围,环路内的单元级数 N 越多越好. 综上所述,为了兼顾电路的测量精度和测量范围,脉宽收缩 TDC 环路中的单元级数 N 需要合理选取,一般根据电路性能指标来确定. 本测量电路是针对数 GHz 时钟信号设计的,其测量范围在 500 ps 内即可,测量精度设计为 1 ps. 根据这些指标,脉宽收缩 TDC 环路最终确定为 5 级单元,前面 4 级输出各接 5 个并联补偿反相器作为负载,以使每级输出负载相等,得到测量范围是 450 ps. 测量精度约为 1 ps. 均满足性能指标.

环路连接方式的优点是可以节省芯片面积. 上一节已经介绍了在脉宽收缩链路中, 脉宽为 T 的时钟信号需要通过  $T/T_{LSB}$  级链接单元才能消失, 而在环路连接方式中, 只需固定数量的 N 个收缩单元, 配以计数器, 译码与控制电路和多路选择器等模块即可完成测量. 在本设计中, 测量范围是 450 ps, 测量精度为 1 ps, 因此链路连接方式的电路至少需要 450 个收缩单元和相同数目的 D 触发器, 共需要 8100 个晶体管; 而环路连接方式中收缩环路需要 5 个收缩单元和 D 触发器, 即 90 个晶体管, 计数器 64 个晶体管, 译码与控制电路 34 个晶体管, 多路选择器 20 个晶体管, 负载 40 个晶体管, 一共 248 个晶体管. 因此, 环路连接方式所需的晶体管数量大约为链路连接方式的 1/32, 即环路连接方式确实可以节省面积开销, 而且所设计的测量范围越大或测量精度越高, 节省的面积也越多, 此即使用环路连接方式的显著优点. 另外, 由于测量环路只使用少量 (10 个)的晶体管, 工艺波动对其造成的影响并不大, 仿真结果也表明工艺偏差对测量系统产生的误差在可接受范围之内. 此外, 为了保证电路的测量精度, 在电源与地之间连接去耦电容, 以减小片上噪声对测量电路的影响.

# 2.3 片上时钟测试电路的实现

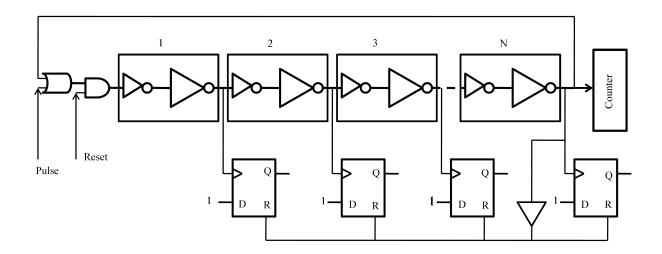

脉宽收缩 TDC 实现了待测脉宽的数字转换,与大多数脉宽测量电路一样,其测量结果仅仅体现一个脉宽的情况,而时钟的抖动需要累积多个周期脉宽的测量结果才能得出,本节将介绍如何把单次测量结果转化为累积测量,直接显示时钟抖动的测量结果.

Figure 3 Structure diagram of on-chip clock jitter testing circuit

以脉宽收缩 TDC 环为核心测量电路, 配以必要的逻辑控制和信号处理电路, 便可实现片上时钟 抖动的监测. 具体结构框图如图 3 所示, 除了脉宽收缩环路模块外, 还包括计数器, 译码与控制电路, 多路选择器, 异或阵列以及累积寄存器等.

由于片内可能存在多路待测时钟信号,因此用多路选择器来接入待测时钟脉冲;根据上一小节的 分析, 脉宽收缩环路最终得到两个输出, 一个是用计数器记录的循环次数, 另一个是触发器记录的环路 最后状态; 译码器根据计数器结果得到相应的控制信号, 用于控制多路选择器, 以使脉宽收缩环路触 发器的输出正确连接到相应的异或阵列端口中,同时将该组端口之前的所有异或端口都接到"1",之 后的端口都接到"0".

异或阵列主要用于检测时钟边沿, 连续的 "1" 或连续的 "0" 进行异或之后都为 "0", 只有在边沿 "10"和 "01"的情况下为 "1", 此即边沿检测原理, 为了获取脉冲的起始边沿, 把异或阵列的第一个输 入固定接"0", 信号处理电路主要是累积寄存器, 它由逻辑门和触发器组成, 在普通模式下, 即 Sticky mode=0, 此时累积寄存器相当于普通的 D 触发器, 异或门的输出直接作为触发器的输入, 当 Clk 信号 有效时, 触发器只输出当次时钟脉冲的测量结果. 图 3 下面给出了某次测量结果与对应待测信号, 由 图可知, 在全 "0" 的数字序列背景中用 "1" 来表示信号的边沿, 能够直观地把时钟脉宽显示出来.

在监测模式下,即 Sticky mode=1, D 触发器的输出和异或门的输出进行或运算后再作为触发器 的输入信号, 形成累积寄存器. 如果累积寄存器上一次输出为"1", 那么无论本次异或运算结果是多 少, 其输出仍然保持为"1"; 而如果累积寄存器上一次输出为"0", 本次异或结果为"1", 那么输出也为 "1". 因此实现了累积多个时钟脉冲的测量结果, 时钟的抖动可从输出数字序列码中直接读出, 这也是

图 4 测试电路的输出数字序列码比特位数与时钟脉宽之间的关系

Figure 4 Relationship between the output digital serial code bits and the clock pulse width

### 表 1 本文的时钟抖动测试电路的性能参数

Table 1 The performance of the proposed clock jitter testing circuit

| Technology | Resolution | Range   | Power | Consumption       | Loop stage |

|------------|------------|---------|-------|-------------------|------------|

| 65 nm      | 1 ps       | 450  ps | 1.2 V | $2.1~\mathrm{mW}$ | 5          |

该测量电路的一大特点. 另外, 需要说明的是图 3 所示的片上时钟测量电路是针对高电平部分脉宽设计的, 对于低电平部分的脉宽, 测量之前通过一个反相器即可, 要求该反相器不能改变信号的脉宽.

# 3 测试电路的仿真结果

本文提出的片上时钟抖动测量电路是在 Cadence Spectre 模拟环境下采用 65 nm CMOS 工艺实现的,根据性能指标搭建一个 5 级收缩单元环路并调试好宽长比,其中前 4 级各接 5 个并联补偿反相器以使负载相等,每一级单元都具有相同的  $T_{LSB}$ ,系统的其他电路都满足相关要求后,对整体电路进行仿真,在电源电压为 1.2~V~ 时,其功耗为 2.1~ mW.

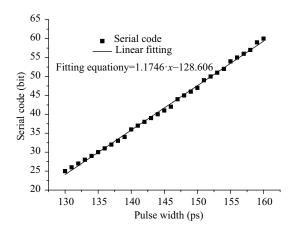

与其他测量工具一样, 为了得到更高的准确性, 需要对测量电路进行定标. 当  $V_{DD}=1.2~V~$  时, 仿真得到输出数字序列码比特位数与时钟脉宽之间的关系如图 4 所示.

图 4 中黑色方点是仿真得到的输出序列码位数, 细线是数据的线性拟合结果, 拟合直线的斜率为 1.17, 即测量精度约为 1 ps. 因此时钟脉宽每变化约 1 ps, 输出序列码的比特位数就会变化 1 bit. 表 1 总结了本文提出的时钟抖动测试电路的各项性能参数.

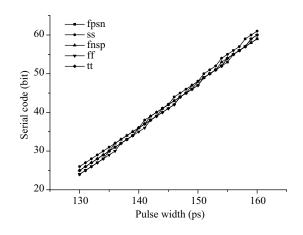

为了分析工艺偏差对本文所设计片上时钟抖动测试电路的影响, 在不同工艺角下仿真输出数字序 列码比特位数与时钟脉宽之间的关系如图 5 所示.

仿真条件为晶体管在不同工艺角下的所有情况. 由图可知, 在不同工艺角下, 所测数据与中心值的偏差在 ±1 bit 之内, 满足系统的指标要求. 因此, 仿真结果证明了工艺波动对测量精度的影响并不大.

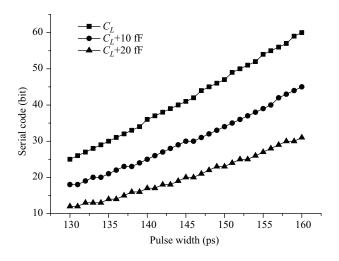

根据公式 (3), 收缩单元的负载会对电路测量精度造成很大影响. 如图 6 给出三种不同负载下的测量结果, 其中方点表示系统在原本最小负载  $C_L$  下的测量结果, 圆点和三角点分别表示在  $C_L + 10 fF$

图 5 不同工艺角下的比特位数与时钟脉宽之间的关系 Figure 5 Relationship between serial code bits and clock pulse width at different corners

图 6 不同负载下比特位数与时钟脉宽之间的关系 Figure 6 Relationship between serial code bits and clock pulse width at different loads

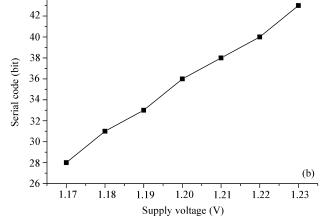

图 7 不同  $V_{\mathrm{DD}}$  下测量相同时钟脉宽得到序列码以及序列码位数与电压关系图

44 -

The serial codes in (a) and relationship between serial code bits and supply voltage in (b) of measuring the same pulse width signal under différent  $V_{\rm DD}$

和  $C_L + 20fF$  下的测量结果. 由图可知, 负载越大, 相同脉宽信号测得的数字序列码位数越小; 分别对 三组数据进行线性拟合, 结果表明: 负载越大, 线性拟合的斜率越小, 即  $T_{LSB}$  越大, 故其测量精度也越 低,与理论推导相符.因此,为了获得更高的测量精度,必须保证环路每级收缩单元的输出负载最小.

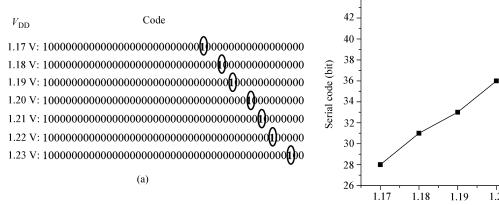

另外, 需要注意的是本测试电路是在电源电压  $V_{DD}=1.2~\mathrm{V}$  情况下进行定标的, 而从式 (3) 可知, 脉宽收缩单元的减小时间是跟  $V_{DD}$  成反比例关系的, 随着  $V_{DD}$  的增大, 压缩单元的减小时间会变小, 脉冲消失前通过的压缩单元数目就会增加, 反之亦然. 因此, 在不同  $V_{DD}$  的情况下仿真测量同样脉宽 (140 ps) 的信号, 得到输出数字序列码比特位数与电源电压之间关系如图 7 所示.

由图 7 可知, 对于同样脉宽的时钟信号, 在不同电源电压下测得的比特位数是不同的, 且随着电 源电压的增加而增加, 电源电压每变化 10 mV, 输出序列码比特位数就会有 2~3 bit 的变化. 因此, 在

## 图 8 在监测模式下测试时钟抖动的输出结果

Figure 8 Output of the clock jitter measurement in monitor-mode

一定电源电压下对系统进行定标后,要保证电源电压的稳定性,否则会影响测量结果.但是反过来也可以利用本系统的这一特点来监测芯片的电源电压,即施加固定脉宽的信号,通过观察电路输出数字序列码的变化情况来监测电源电压的抖动.

下面仿真电路的时钟抖动监测功能. 此时控制信号 Sticky mode=1, 设置待测时钟信号频率为 3.5 GHz, 占空比为 50%, 那么时钟周期约为 286 ps, 脉宽为 143 ps. 在  $V_{\rm DD}$ =1.2 V 的条件下仿真 100 个时钟周期, 测得无抖动时钟信号和注入 1 ps 抖动, 注入 2 ps 抖动, 注入 3 ps 抖动时钟信号的输出数字序列码分别如图 8 所示.

测量结果表明,本电路在监测模式下的输出数字序列码能够直观地反映时钟的抖动情况,当序列码只有一个"1"(虚线框内)时,说明所测周期内时钟脉冲宽度都相等,即时钟不存在抖动;若序列码产生连续的"1"(虚线框内),则说明所测周期内时钟脉冲宽度并非完全一致,时钟存在抖动,其抖动大小也可以直接读出,因此实现了片上时钟抖动监测的功能.而普通时钟测量 TDC 电路测量时钟信号抖动时,由于每次只输出单个周期的测量结果,无法直接从输出结果中读出时钟抖动.对比两种测量电路的输出结果可知,本文提出的电路在测量片上时钟抖动时可以直接显示抖动大小,明显优于普通的时钟测量 TDC 电路.

# 4 结论

本文提出一种基于脉宽收缩和累积寄存器的高精度片上时钟抖动测试电路,用于监测芯片内部时钟信号的抖动.该测试电路是根据脉宽收缩 TDC 原理设计的,将脉宽收缩单元以环状的方式连接起来,可提高每个收缩单元的利用率,大大节省芯片面积开销.对脉宽收缩环的输出进行异或运算,并用累积寄存器将多次运算结果同时记录下来,最后可直接输出时钟信号的抖动.该测试电路采用 65 nm CMOS 工艺设计,仿真结果表明,电源电压为 1.2 V 时,测量精度为 1 ps,达到该工艺下目前报道的最高测量精度的量级.在监测模式下分别模拟了 100 个周期的无抖动时钟信号和注入抖动的时钟信号,该测试电路可直观地显示多个周期的时钟抖动,与普通时钟测量 TDC 电路相比,具有明显的优势.

# 参考文献 -

- 1 ITRS. International Technology Roadmap for Semiconductors. 2013

- 2 Udaya N. Test challenges for SONET/SDH physical layer OC3 devices and beyond. In: Proceedings of IEEE International Test Conference (ITC), Baltimore, 2001. 502–511

- 3 Cole C B, Warwick T P. High speed digital transceivers: a challenge for manufacturing. In: Proceedings of IEEE International Test Conference (ITC), Atlantic City, 1999. 211–215

- 4 Chan A H, Roberts G W. A jitter characterization system using a component-invariant vernier delay line. IEEE Trans VLSI Syst, 2004, 12: 79–95

- 5 Staszewski R B, Vemulapalli S, Vallur P, et al. 1.3V 20ps time-to-digital converter for frequency synthesis in 90-nm CMOS. IEEE Trans Circuits-II, 2006, 53: 220–224

- 6 Yao C Y, Hsia W C, Tsai P J, et al. The vernier-based TDC employing soft-injection-locked ring oscillators. In: Proceedings of IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Graz, 2012. 2291–2294

- 7 Chen P, Zheng J C, Chen C C. A monolithic vernier-based time-to-digital converter with dual PLLs for self-calibration. In: Proceedings of IEEE Custom Integrated Circuits Conference (CICC), San Jose, 2005. 321–324

- 8 Rashidzadeh R, Ahmadi M, Miller W C. An all-digital self-calibration method for a vernier-based time-to-digital converter. IEEE Trans Instrum Meas, 2010, 59: 463–469

- 9 Lu P, Liscidini A, Andreani P. A 3.6mW, 90nm CMOS gated-vernier time-to-digital converter with an equivalent resolution of 3.2ps. IEEE J Solid-St Circ, 2012, 47: 1626–1635

- 10 Tamborini D, Markovic B, Tisa S, et al. TDC with 1.5% DNL based on a single-stage vernier delay-loop fine interpolation. In: Proceedings of IEEE Nordic-Mediterranean Workshop on Time-to-Digital Converters (NoMe TDC), Perugia, 2013. 1–6

- 11 Henzler S, Koeppe S, Kamp W, et al. 90nm 4.7ps–Resolution 0.7-LSB single-shot precision and 19pJ-per-shot local passive interpolation time-to-digital converter with on-chip characterization. In: Proceedings of Solid-State Circuits Conference, San Francisco, 2008. 548–635

- 12 Minjae L, Abidi A A. A9b, 1.25ps resolution coarse-fine timeto-digital converter in 90nm CMOS that amplifies a time residue. In: Proceedings of IEEE JSSC, 2008

- 13 Mandai S, Iizuka T, Nakura T, et al. Time-to-digital converter based on time difference amplifier with non-linearity calibration. In: Proceedings of the IEEE ESSCIRC, Seville, 2010. 266–269

- 14 Chen C C, Lin S H, Hwang C S. An area-efficient CMOS time-to-digital converter based on a pulse-shrinking scheme. IEEE Trans Circuits-II, 2014, 61: 163–167

- 15 Liu Y, Vollenbruch U, Chen Y J, et al. A 6ps resolution pulse shrinking time-to-digital converter as phase detector in multi-mode transceiver. In: Proceedings of IEEE Radio and Wireless Symposium, Orlando, 2008. 163–166

- 16 Chen P, Liu S I, Wu J S. A low power high accuracy CMOS time-to-digital converter. In: Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS), Hong Kong, 1997. 281–284

- 17 Karadamoglou K, Paschalidis N P, Sarris E, et al. An 11-bit high-resolution and adjustable-range CMOS time-to-digital converter for space science instruments. IEEE J Solid-St Circ, 2004, 39: 214–222

- 18 Franch R, Restle P, James N, et al. On-chip timing uncertainty measurements on IBM microprocessors. In: Proceedings of IEEE International Test Conference (ITC), Santa Clara, 2007. 1–7

# On-chip clock jitter testing circuit based on pulse-shrinkage and accumulation register

FENG WeiLei<sup>1</sup>, FENG JianHua<sup>1,2\*</sup>, YE HongFei<sup>2</sup> & ZHANG Xing<sup>1,2</sup>

- 1 Shenzhen Graduate School of Peking University, Shenzhen 518055, China;

- 2 Institute of Microelectronics, Peking University, Beijing 100871, China

- \*E-mail: fengjh@pku.edu.cn

Abstract An on-chip clock jitter testing circuit based on pulse-shrinkage TDC and accumulation register is introduced in this paper, which can be used to monitor the jitter of internal clock signal with sub-gate delay resolution. The whole testing circuit is consisted of pulse-shrinkage loop, accumulation register, XOR array, counter and control circuit. All the pulse-shrinkage units are connected in a loop to reduce the required number, so that the area can be saved and the effects of process variations can be reduced. Multi-cycle clock pulse measurement results are accumulated simultaneously and output in the form of serial code in monitor-mode, the clock jitter can be read directly from the serial code. The whole circuit is designed in a 65-nm CMOS process, simulation

results show that the circuit can measure several GHz clock signal, with a resolution of 1 ps.

Keywords pulse-shrinkage, clock jitter, on-chip measurement, jitter testing, accumulation register

FENG WeiLei was born in 1989. He received the B.E. degree from School of Physics and Engineering, Sun Yat-Sen University, Guangzhou, in 2012. Currently, he is a postgradute student in Shenzhen Graduate School of Peking University. His main research interests include SOC test and SerDes test.

FENG JianHua was born in 1963. He received the Ph.D. degree in microelectronics from the Xi'an Microelectronics Technology Institute, Xian, China, in 2000. Currently, he is an Associate Professor at Peking University. His research interests include VLSI test and design for testability, design for reliability and hardware security.

YE HongFei was born in 1972. He received the M.S. degree in microelectronics from Peking University, Beijing, China, in 1997. Currently, he is an engineer working on SOC testing and microelectronic device measurement in the Institute of Microelectronics, Peking University.

ZHANG Xing was born in 1965. He received the Ph.D. degree in microelectronics from Shaanxi Microelectronics Institute, Shaanxi, in 1993. Currently, he is a Professor in the Institute of Microelectronics, Peking University, Beijing. His current research interests include the physics and new structures of nano-scaled MOS devices, CMOS IC design and process technology.